REV. 0

AD1887

–14–

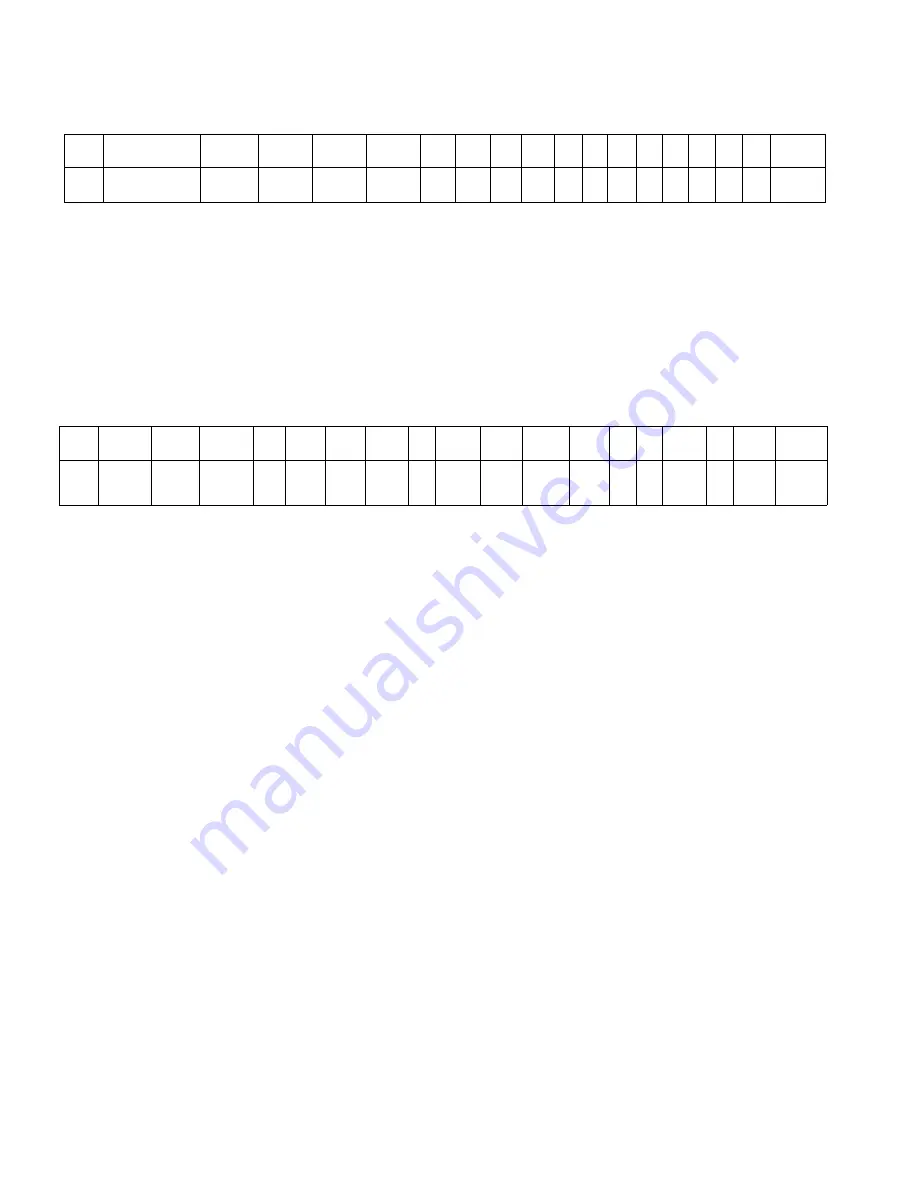

Serial Configuration (Index 74h)

g

e

R g

e

R g

e

R g

e

R g

e

R

m

u

N m

u

N m

u

N m

u

N m

u

N

e

m

a

N

e

m

a

N

e

m

a

N

e

m

a

N

e

m

a

N

5

1

D 5

1

D 5

1

D 5

1

D 5

1

D

4

1

D 4

1

D 4

1

D 4

1

D 4

1

D

3

1

D 3

1

D 3

1

D 3

1

D 3

1

D

2

1

D 2

1

D 2

1

D 2

1

D 2

1

D

1

1

D 1

1

D 1

1

D 1

1

D 1

1

D

0

1

D 0

1

D 0

1

D 0

1

D 0

1

D

9

D9

D9

D9

D9

D

8

D8

D8

D8

D8

D

7

D7

D7

D7

D7

D

6

D6

D6

D6

D6

D

5

D5

D5

D5

D5

D

4

D4

D4

D4

D4

D

3

D3

D3

D3

D3

D

2

D2

D2

D2

D2

D

1

D1

D1

D1

D1

D

0

D0

D0

D0

D0

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

h

4

7 h

4

7 h

4

7 h

4

7 h

4

7

l

a

i

r

e

S

l

a

i

r

e

S

l

a

i

r

e

S

l

a

i

r

e

S

l

a

i

r

e

S

n

o

i

t

a

r

u

g

i

f

n

o

C

n

o

i

t

a

r

u

g

i

f

n

o

C

n

o

i

t

a

r

u

g

i

f

n

o

C

n

o

i

t

a

r

u

g

i

f

n

o

C

n

o

i

t

a

r

u

g

i

f

n

o

C

6

1

T

O

L

S

6

1

T

O

L

S

6

1

T

O

L

S

6

1

T

O

L

S

6

1

T

O

L

S

2

M

G

E

R

2

M

G

E

R

2

M

G

E

R

2

M

G

E

R

2

M

G

E

R

1

M

G

E

R

1

M

G

E

R

1

M

G

E

R

1

M

G

E

R

1

M

G

E

R

0

M

G

E

R

0

M

G

E

R

0

M

G

E

R

0

M

G

E

R

0

M

G

E

R

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

h

0

0

0

7

h

0

0

0

7

h

0

0

0

7

h

0

0

0

7

h

0

0

0

7

Note: This register is not reset when the reset register (Register 00h) is written.

DHWR

Disable Hardware Reset.

REGM0

Master Codec Register Mask.

REGM1

Slave 1 Codec Register Mask.

REGM2

Slave 2 Codec Register Mask.

SLOT16

Enable 16-bit slots.

If your system uses only a single AD1887, you can ignore the register mask bits.

SLOT16 makes all AC Link slots 16 bits in length, formatted into 16 slots.

Miscellaneous Control Bits (Index 76h)

g

e

R g

e

R g

e

R g

e

R g

e

R

m

u

N m

u

N m

u

N m

u

N m

u

N

e

m

a

N

e

m

a

N

e

m

a

N

e

m

a

N

e

m

a

N

5

1

D 5

1

D 5

1

D 5

1

D 5

1

D

4

1

D 4

1

D 4

1

D 4

1

D 4

1

D

3

1

D 3

1

D 3

1

D 3

1

D 3

1

D

2

1

D 2

1

D 2

1

D 2

1

D 2

1

D

1

1

D 1

1

D 1

1

D 1

1

D 1

1

D

0

1

D 0

1

D 0

1

D 0

1

D 0

1

D

9

D9

D9

D9

D9

D

8

D8

D8

D8

D8

D

7

D7

D7

D7

D7

D

6

D6

D6

D6

D6

D

5

D5

D5

D5

D5

D

4

D4

D4

D4

D4

D

3

D3

D3

D3

D3

D

2

D2

D2

D2

D2

D

1

D1

D1

D1

D1

D

0

D0

D0

D0

D0

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

t

l

u

a

f

e

D

h

6

7 h

6

7 h

6

7 h

6

7 h

6

7

c

s

i

M c

s

i

M c

s

i

M c

s

i

M c

s

i

M

l

o

r

t

n

o

C

l

o

r

t

n

o

C

l

o

r

t

n

o

C

l

o

r

t

n

o

C

l

o

r

t

n

o

C

s

t

i

B s

t

i

B s

t

i

B s

t

i

B s

t

i

B

Z

C

A

D

Z

C

A

D

Z

C

A

D

Z

C

A

D

Z

C

A

D

X

I

M

P

L

X

I

M

P

L

X

I

M

P

L

X

I

M

P

L

X

I

M

P

L

X

X

X

X

X

M

A

D M

A

D M

A

D M

A

D M

A

D

S

M

D

S

M

D

S

M

D

S

M

D

S

M

D

R

S

L

D

R

S

L

D

R

S

L

D

R

S

L

D

R

S

L

D

X

X

X

X

X

R

S

L

A

R

S

L

A

R

S

L

A

R

S

L

A

R

S

L

A

D

O

M D

O

M D

O

M D

O

M

D

O

M

N

EN

EN

EN

EN

E

0

1

X

R

S

0

1

X

R

S

0

1

X

R

S

0

1

X

R

S

0

1

X

R

S

7

D7

D7

D7

D7

D

8

X

R

S

8

X

R

S

8

X

R

S

8

X

R

S

8

X

R

S

7

D7

D7

D7

D7

D

X

X

X

X

X

X

X

X

X

X

R

S

R

D

R

S

R

D

R

S

R

D

R

S

R

D

R

S

R

D

X

X

X

X

X

R

S

R

A

R

S

R

A

R

S

R

A

R

S

R

A

R

S

R

A

h

4

0

4

0

h

4

0

4

0

h

4

0

4

0

h

4

0

4

0

h

4

0

4

0

ARSR

ADC Right Sample Generator Select

0 = SR0 Selected (32h)

1 = SR1 Selected (2Ch)

DRSR

DAC Right Sample Generator Select

0 = SR0 Selected (32h)

1 = SR1 Selected (2Ch)

SRX8D7

Multiply SR1 rate by 8/7.

SRX10D7

Multiply SR1 rate by 10/7. SRX10D7 and SRX8D7 are mutually exclusive; SRX10D7 has priority if both are set.

MODEN

Modem filter enable (left channel only). Change only when DACs are powered down.

ALSR

ADC Left Sample Generator Select

0 = SR0 Selected (32h)

1 = SR1 Selected (2Ch)

DLSR

DAC Left Sample Generator Select

0 = SR0 Selected (32h)

1 = SR1 Selected (2Ch)

DMS

Digital Mono Select

0 = Mixer

1 = Left DAC + Right DAC

DAM

Digital Audio Mode. DAC Outputs bypass analog mixer and sent directly to the codec output.

LPMIX

Low-Power Mixer

DACZ

Zero-fill (vs. repeat) if DAC is starved for data.