REV. 0

AD1887

–5–

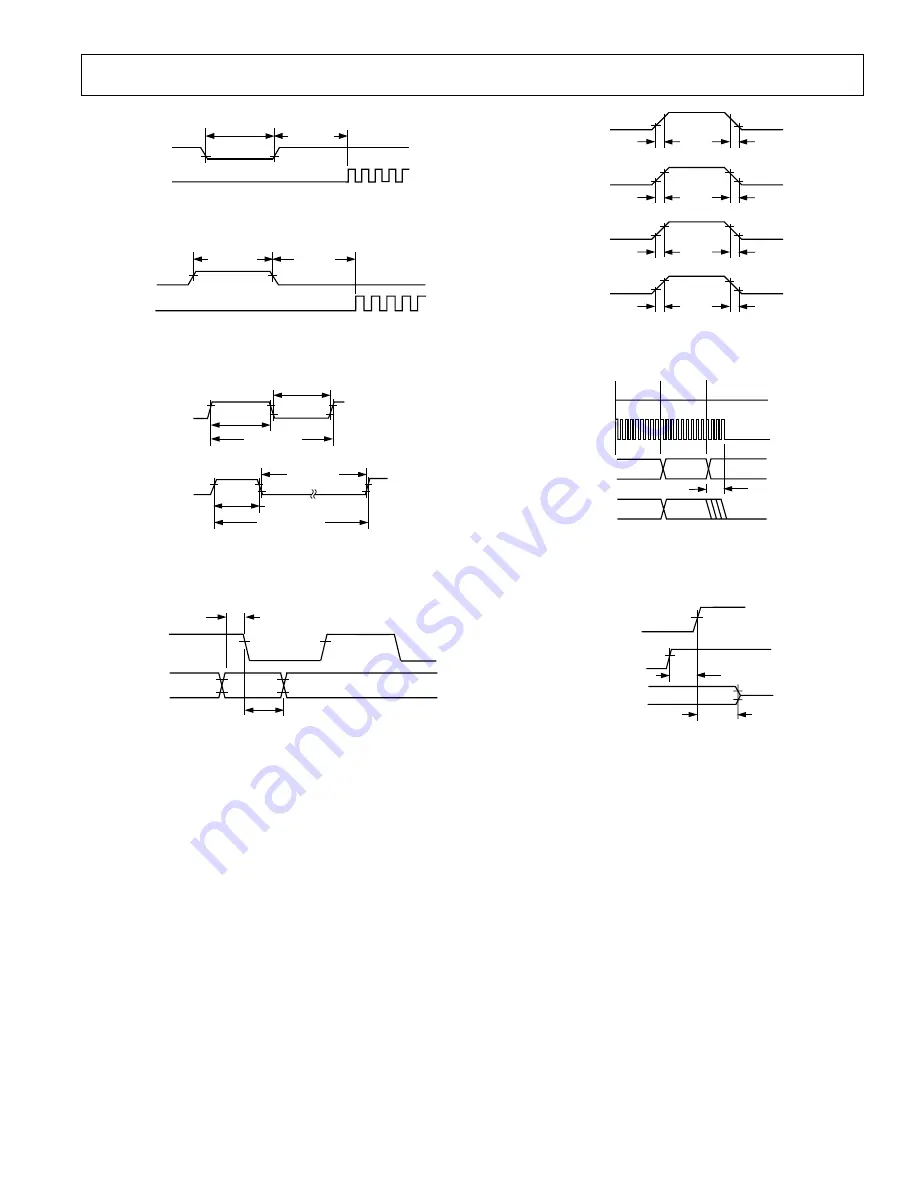

RESET

BIT_CLK

t

RST2CLK

t

RST_LOW

Figure 1. Cold Reset

SYNC

BIT_CLK

t

SYNC_HIGH

t

RST2CLK

Figure 2. Warm Reset

t

CLK_HIGH

BIT_CLK

t

CLK_LOW

SYNC

t

SYNC_HIGH

t

SYNC_LOW

t

SYNC_PERIOD

t

CLK_PERIOD

Figure 3. Clock Timing

BIT_CLK

SYNC

t

HOLD

SDATA_OUT

t

SETUP

Figure 4. Data Setup and Hold

BIT_CLK

SYNC

SDATA_IN

t

RISECLK

t

RISESYNC

t

RISEDIN

t

RISEDOUT

t

FALLCLK

t

FALLSYNC

t

FALLDIN

t

FALLDOUT

SDATA_OUT

Figure 5. Signal Rise and Fall Time

BIT_CLK

SDATA_OUT

SYNC

SDATA_IN

SLOT 1

SLOT 2

WRITE

TO 0x26

DATA

PR4

DON’T

CARE

t

S2_PDOWN

NOTE: BIT_CLK NOT TO SCALE

Figure 6. AC Link Low Power Mode Timing

RESET

SDATA_OUT

HI-Z

t

SETUP2RST

t

OFF

SDATA_IN, BIT_CLK

Figure 7. ATE Test Mode