AD9643/AD9613/AD6649/AD6643 User Guide

UG-293

Rev. A | Page 3 of 26

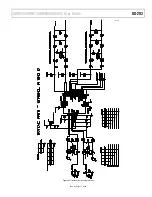

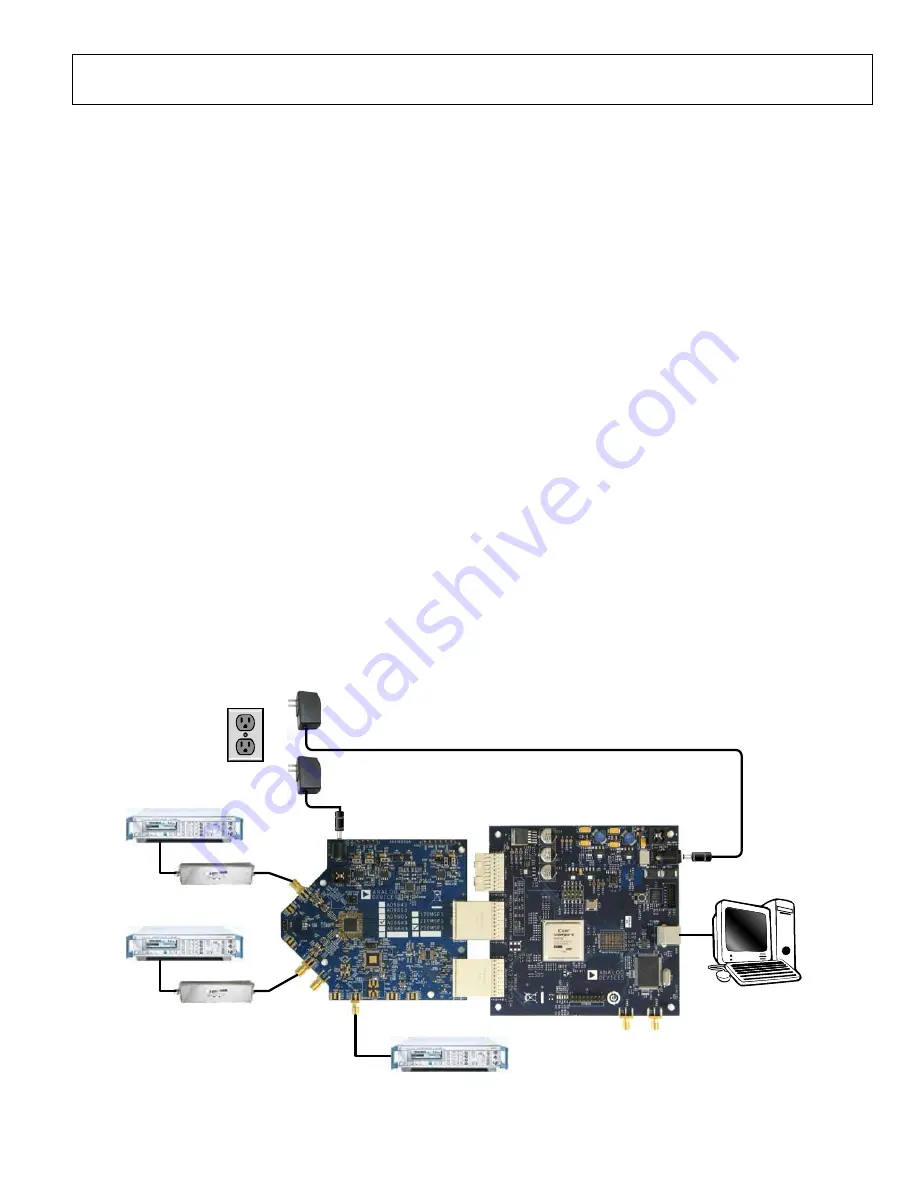

EVALUATION BOARD HARDWARE

The

AD9643

,

AD9613

,

AD6649

, or

AD6643

evaluation board

provides all of the support circuitry required to operate these

devices in their various modes and configurations. Figure 2 shows

the typical bench characterization setup used to evaluate the ac

performance of the

AD9643

,

AD9613

,

AD6649

, or

AD6643

. It is

critical that the signal sources used for the analog input and the

clock have very low phase noise (<1 ps rms jitter) to achieve the

optimum performance of the signal chain. Proper filtering of

the analog input signal to remove harmonics and lower the inte-

grated or broadband noise at the input is necessary to achieve

the specified noise performance.

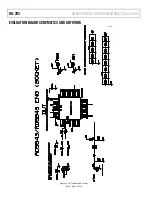

See the Evaluation Board Software Quick Start Procedures section

to get started, and see Figure 23 to Figure 34 for the complete

schematics and layout diagrams. These diagrams demonstrate

the routing and grounding techniques that should be applied at

the system level when designing application boards using these

converters.

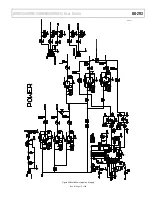

POWER SUPPLIES

This evaluation board comes with a wall-mountable switching

power supply that provides a 6 V, 2 A maximum output. Connect

the supply to a rated 100 V ac to 240 V ac wall outlet at 47 Hz

to 63 Hz. The output from the supply is provided through a

2.1 mm inner diameter jack that connects to the printed circuit

board (PCB) at P201. The 6 V supply is fused and conditioned

on the PCB before connecting to the low dropout (LDO) linear

regulators (default configuration) that supply the proper bias to

each of the various sections on the board.

The evaluation board can be powered in a nondefault condition

using external bench power supplies. To do this, remove the

jumpers on the P103, P104, P107, P108, and P105 header pins to

disconnect the outputs from the on-board LDO regulators, which

enables the user to bias each section of the board individually.

Use P202 and P203 to connect a different supply for each section.

A 1.8 V supply is needed with a 1 A current capability for

DUT_AVDD and DRVDD; however, it is recommended that

separate supplies be used for both analog and digital domains.

An additional supply is also required to supply 1.8 V for digital

support circuitry on the board, DVDD. This supply must also

have a 1 A current capability and can be combined with DRVDD

with little or no degradation in performance. To operate the

evaluation board using the SPI and alternate clock options, a

separate 3.3 V analog supply is needed in addition to the other

supplies. This 3.3 V supply, or 3P3V_ANALOG, must have a

1 A current capability. This 3.3 V supply is also used to support

the optional input path amplifier (

ADL5202

) on Channel A and

Channel B.

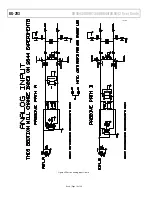

INPUT SIGNALS

When connecting the clock and analog source, use clean signal

generators with low phase noise, such as the Rohde & Schwarz

SMA or HP 8644B signal generators or an equivalent. Use a 1 m,

shielded, RG-58, 50 Ω coaxial cable for connecting to the evalua-

tion board. Enter the desired frequency and amplitude (see the

Specifications section in the data sheet of the respective device).

ANALOG INPUT

PC

RUNNING ADC

ANALYZER

OR VISUAL ANALOG

USER SOFTWARE

SWITCHING

POWER

SUPPLY

SWITCHING

POWER

SUPPLY

6V DC

2A MAX

6V DC

2A MAX

WALL OUTLET

100V TO 240V AC

47Hz TO 63Hz

SIGNAL

SYNTHESIZER

ANALOG INPUT

SIGNAL

SYNTHESIZER

OPTIONAL CLOCK SOURCE

SIGNAL

SYNTHESIZER

09

94

0-

00

2

Figure 2. Evaluation Board Connection