UG-293

AD9643/AD9613/AD6649/AD6643 User Guide

Rev. A | Page 6 of 26

EVALUATION BOARD SOFTWARE QUICK START PROCEDURES

This section provides quick start procedures for using the

AD9643

/

AD9613

/

AD6649

/

AD6643

evaluation board. Both the default

and optional settings are described.

CONFIGURING THE BOARD

Before using the software for testing, configure the evaluation

board as follows:

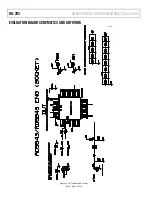

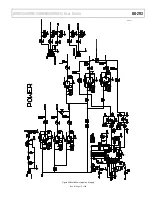

1.

Connect the evaluation board to the data capture board, as

shown in Figure 1 and Figure 2.

2.

Connect one 6 V, 2 A switching power supply (such as the

CUI, Inc., EPS060250UH-PHP-SZ that is supplied) to the

AD9643

/

AD9613

/

AD6649

/

AD6643

board.

3.

Connect another 6 V, 2 A switching power supply (such

as the CUI EPS060250UH-PHP-SZ that is supplied) to the

HSC-ADC-EVALCZ

board.

4.

Connect the

HSC-ADC-EVALCZ

board (J6) to the PC

with a USB cable.

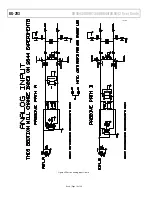

5.

On the ADC evaluation board, confirm that jumpers are

installed on the P105, P108, P104, P107, P110, and P103

headers.

6.

Connect a low jitter sample clock to Connector J506.

7.

Use a clean signal generator with low phase noise to provide

an input signal to the desired channel(s) at Connector J301

(Channel A) and/or Connector J303 (Channel B). Use a

1 m, shielded, RG-58, 50 Ω coaxial cable to connect the

signal generator. For best results, use a narrow-band band-

pass filter with 50 Ω terminations and an appropriate

center frequency. (Analog Devices uses TTE, Allen Avionics,

and K&L band-pass filters.)

USING THE SOFTWARE FOR TESTING

Setting Up the ADC Data Capture

After configuring the board, set up the ADC data capture using

the following steps:

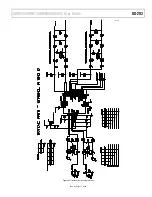

1.

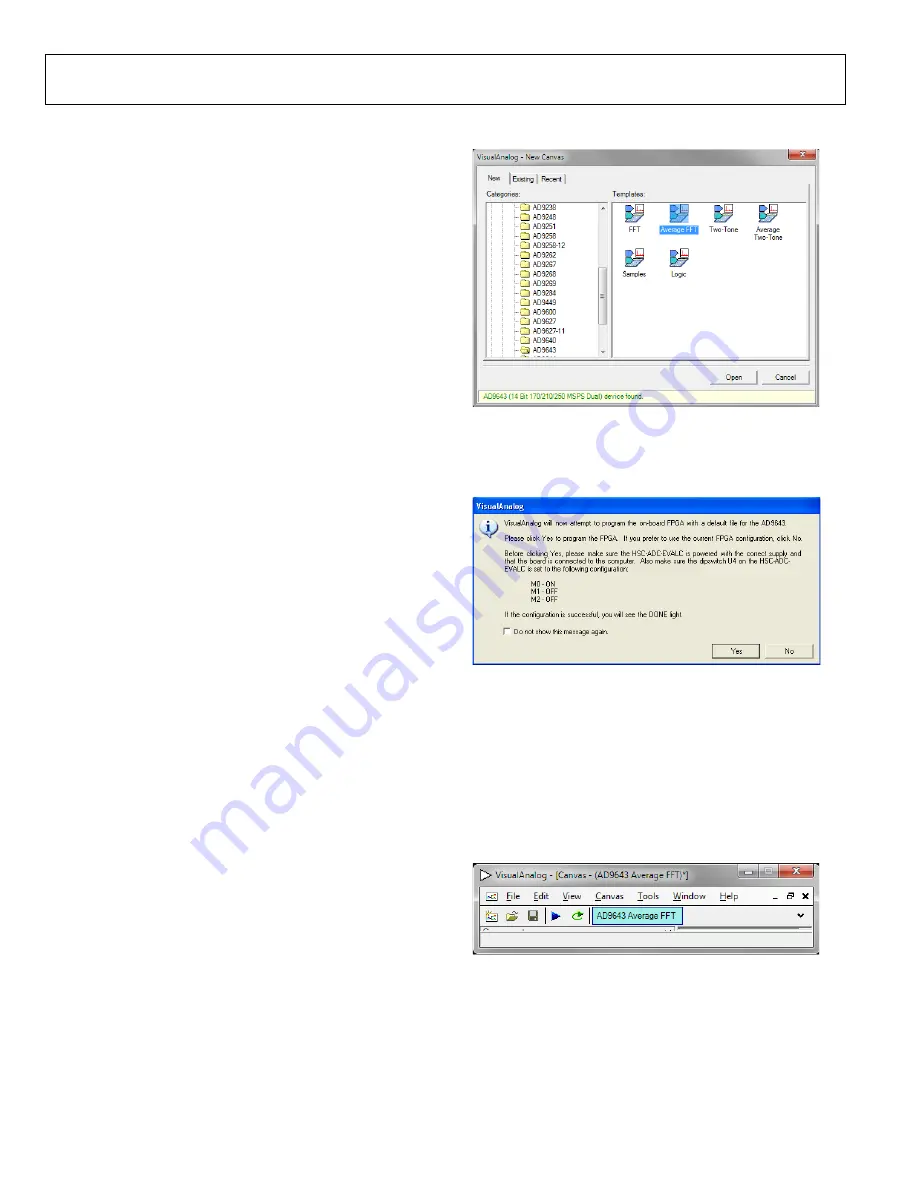

Open VisualAnalog® on the connected PC. The appro-

priate device type should be listed in the status bar of the

VisualAnalog – New Canvas

window. Select the template

that corresponds to the type of testing to be performed

(see Figure 4 where the

AD9643

is shown as an example).

The

AD9643

is given as an example in this user guide.

Similar settings are used for the

AD9613

. For the

AD6649

and

AD6643

, the differences are noted where necessary in

the steps that follow.

0

9940-

004

Figure 4. VisualAnalog, New Canvas Window

2.

After the template is selected, a message appears asking if

the default configuration can be used to program the FPGA

(see Figure 5). Click

Yes

, and the window closes.

09

94

0-

0

05

Figure 5. VisualAnalog Default Configuration Message

3.

To change features to settings other than the default

settings, click the

Expand Display

button, located on the

bottom right corner of the window, to see the main

window that is shown in Figure 7.

4.

Detailed instructions for changing the features and capture

settings can be found in the

AN-905 Application Note

,

VisualAnalog Converter Evaluation Tool Version 1.0 User

Manual

. After the changes are made to the capture settings,

click the

Collapse Display

button (see Figure 6).

09

94

0-

0

06

Figure 6. VisualAnalog Window Toolbar, Collapsed Display