Rev 05 Jun 2013 16:37 | Page 5

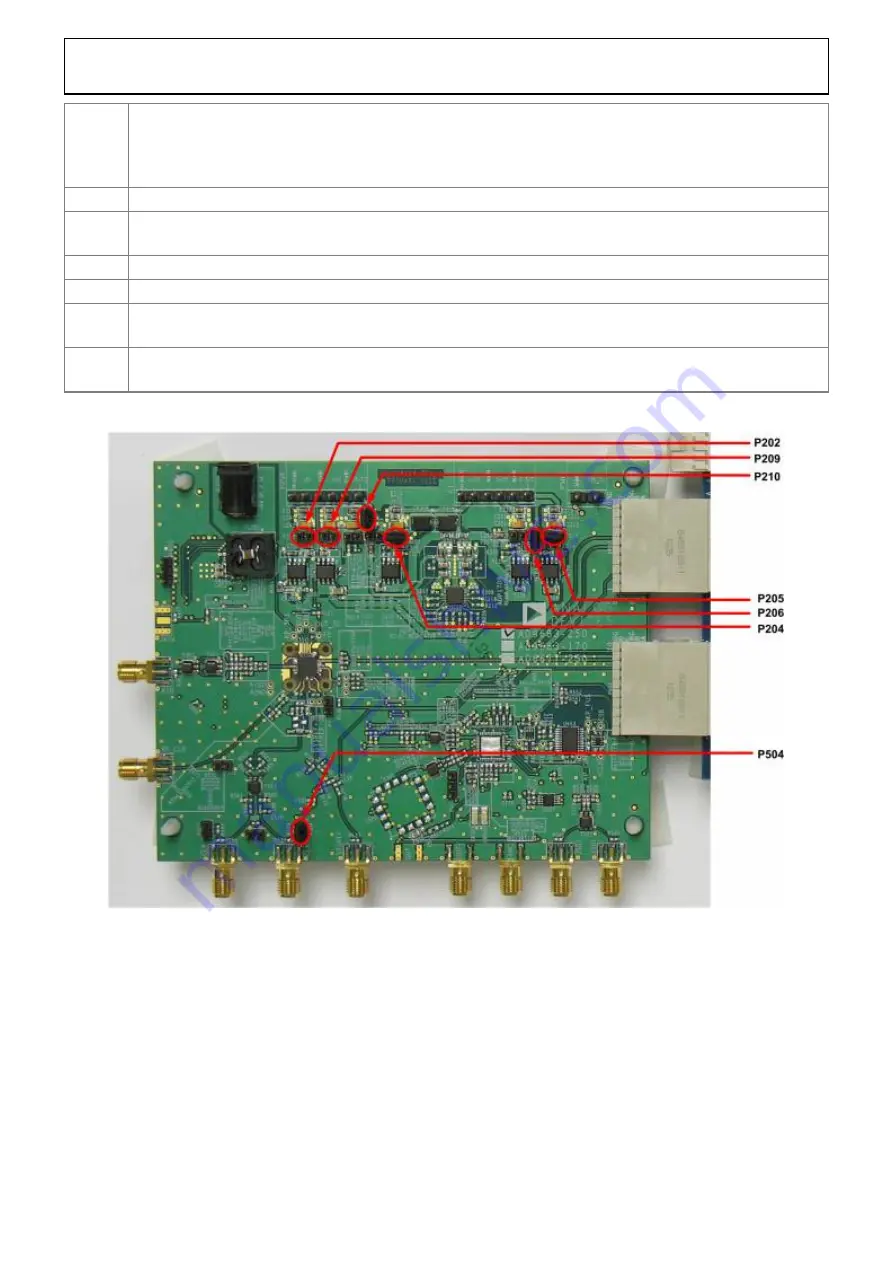

P202

This jumper sets up the 5.0 V power supply voltage for the outputs of the on-board

.

to work properly, its outputs must be tied to a 5.0 V power supply via the

appropriate sized inductors. On the

boards

these inductors are 1 uH.

P209

This jumper sets up the 3.3V analog power supply voltage for the

.

P210

This jumper connects the DVDD power supply domain to the DRVDD power supply domain to

power the JESD204B output drivers of the

and

P205

This jumper connects the AVDD power supply domain of the

.

P206

This jumper connects the DVDD power supply domain of the

P204

This jumper sets up a 3.3 V digital power supply voltage for the

and also powers SPI

related circuitry.

P504

This jumper connects the

external clock input to the reference clock

input of the FPGA (for the JESD204B link) on the

.

Figure 2. Default Jumper Connections for

Evaluation Board Circuitry

This section explains the default and optional settings or modes allowed on the

,

boards.