Rev 13 Nov 2013 01:51 | Page 13

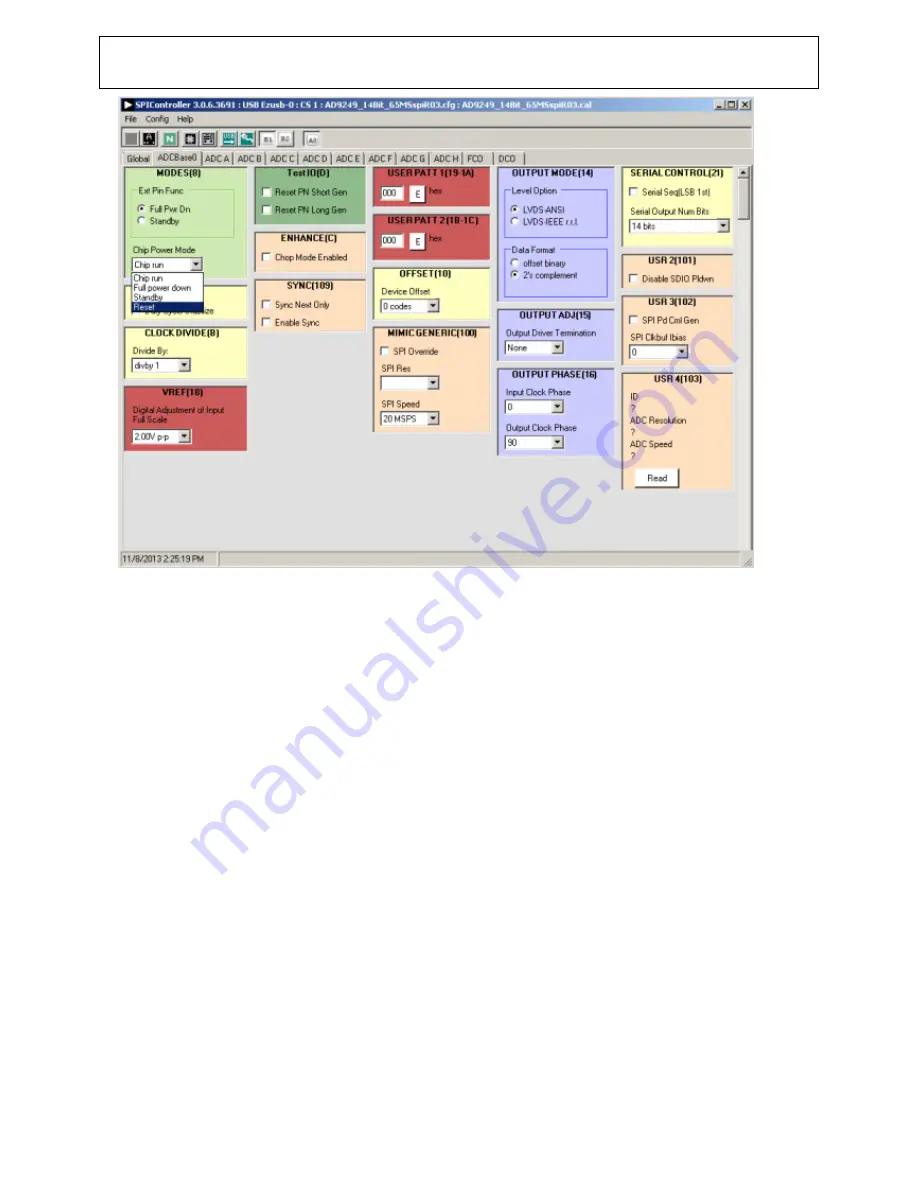

Figure

10. SPI Controller, Chip Power Mode - Digital Reset Selection

Note that other settings can be changed on the ADCBase 0 tab (see Figure 9) and the ADC A

4.

through ADC H tabs (see Figure 11) to set up the part in the desired mode. The ADCBase 0 tab

settings affect the entire part, whereas the settings on the ADC A through ADC H tabs each affect

the selected channel only. The B1 (Bank1), B2 (Bank2) and All buttons at the right end of the

SPIController button row (as seen in Figure 10 and Figure 11) determine which bank of ADCs is

affected by the SPIController settings. The All button is pushed by default which means that the

ADCBase 0 tab settings affect all channels on both ADC banks. The settings in the ADC A through

ADC H will likewise affect their respective channels in both banks. For example, with the All button

pushed, settings in the ADC A tab will affect channels A1 and A2. If the All button is un-pushed and

the B1 (Bank1) button remains pushed, the settings in the ADC A tab will only affect channel A1.

See the data sheet, the

AN-878 Application Note

, High Speed ADC SPI Control Software, and the

AN-877 Application Note

, Interfacing to High Speed ADCs via SPI, for additional information on the

available settings.