Rev 13 Nov 2013 01:51 | Page 9

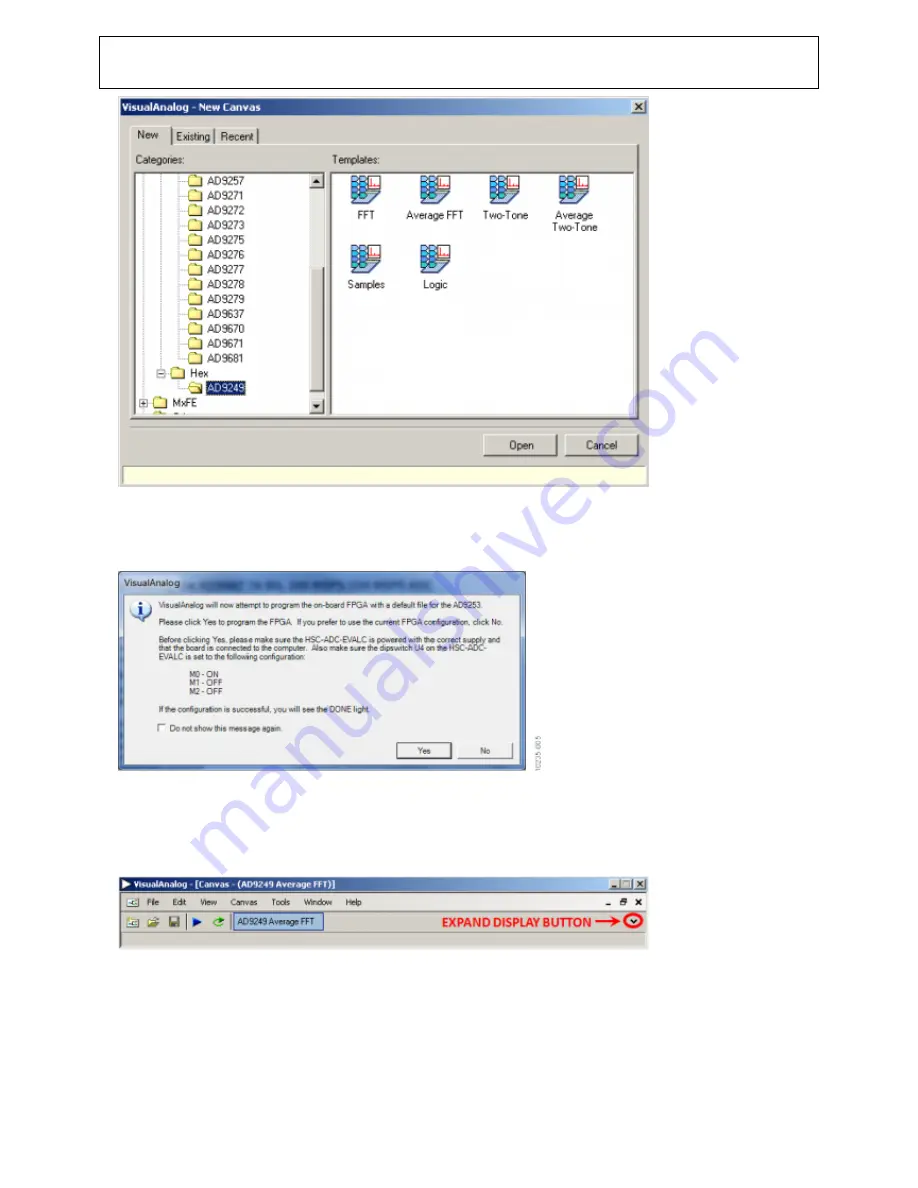

Figure 3. VisualAnalog,

New Canvas Window

After the template is selected, a message might appear asking if the default configuration can be

2.

used to program the FPGA (see Figure 4). If this message appears, click Yes, and the window will

close.

Figure 4. VisualAnalog Default

Configuration Message

To change features to settings other than the default settings, click the Expand Display button,

3.

located on the bottom right corner of the window (see Figure 5), to see what is shown in Figure 6.

Change the features and capture settings by consulting the detailed instructions in the

AN-905

4.

Application Note

, VisualAnalog Converter Evaluation Tool Version 1.0 User Manual.

Figure 5. VisualAnalog Window Toolbar, Collapsed Display