Rev 13 May 2013 17:57 | Page 11

via SPI.

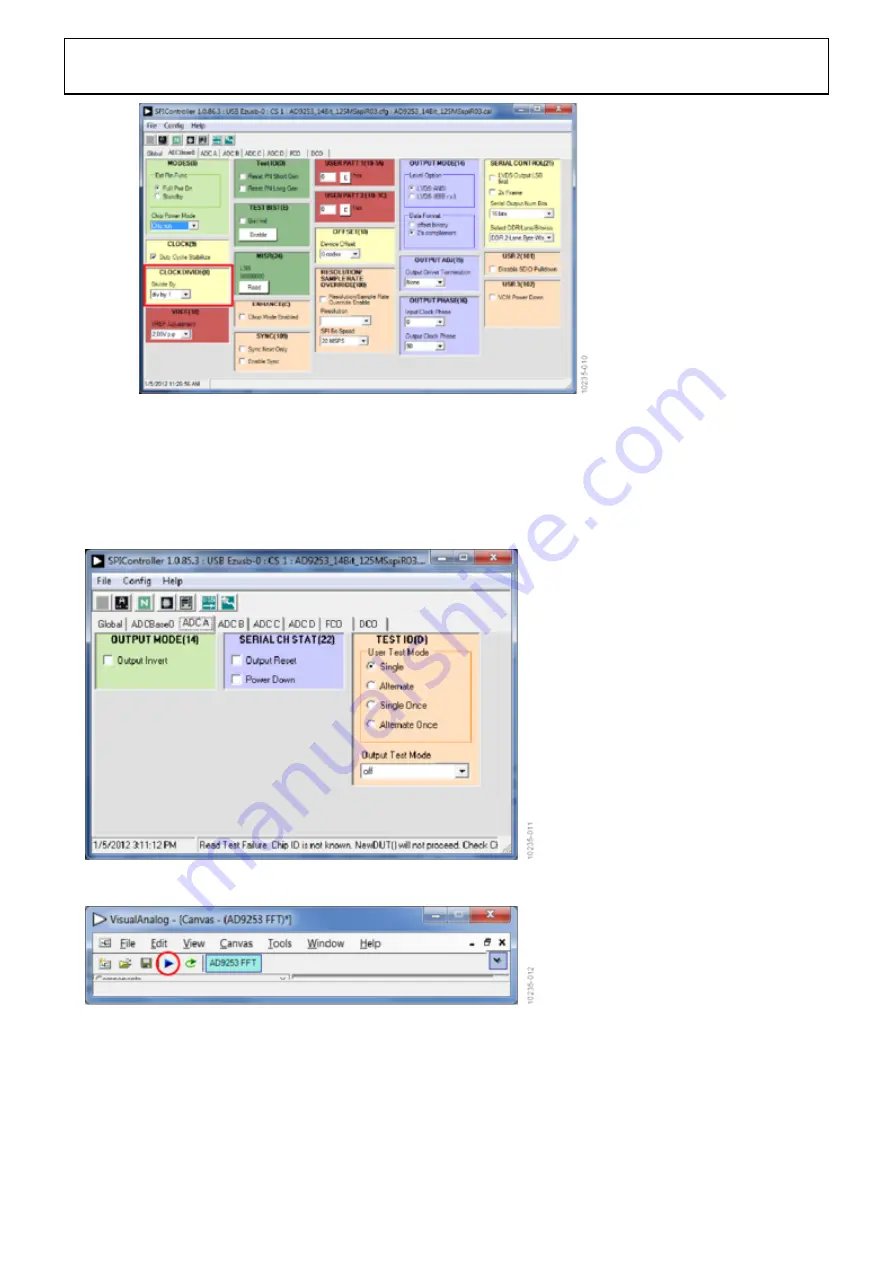

Figure 9. SPI Controller, CLOCK

DIVIDE(B) Box

Note that other settings can be changed on the ADCBase 0 tab (see Figure 9) and the ADC A,

4.

ADC B, ADC C, and ADC D tabs (see Figure 10) to set up the part in the desired mode. The

ADCBase 0 tab settings affect the entire part, whereas the settings on the ADC A, ADC B, ADC C,

and ADC D tabs affect the selected channel only. See the appropriate part data sheet, the

, High Speed ADC SPI Control Software, and the

Interfacing to High Speed ADCs via SPI, for additional information on the available settings.

Figure 10. SPI Controller, Example

ADC A Page

Click the Run button in the VisualAnalog toolbar (see Figure 11).

5.

Figure 11. Run Button (Encircled in

Red) in VisualAnalog Toolbar, Collapsed Display

Adjusting the Amplitude of the Input Signal

The next step is to adjust the amplitude of the input signal for each channel as follows: