Rev 20 Feb 2014 17:53 | Page 16

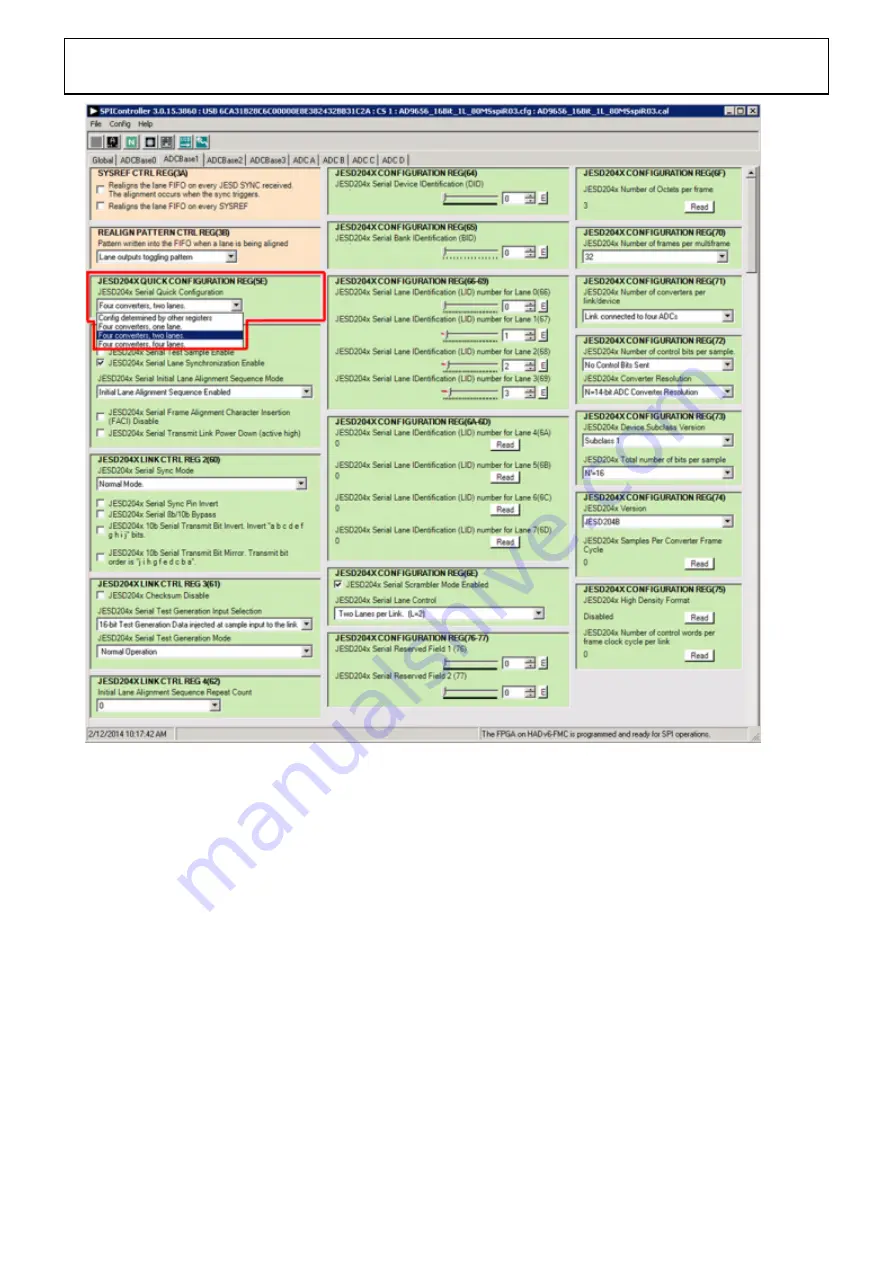

Figure

15. SPI Controller, Quick Configure Box

Note that other settings can be changed on the ADCBase0 tab (see Figure 13) and the ADC A

5.

through ADC D tabs (see Figure 16) to set up the part in the desired mode. The ADCBase0 tab

settings affect the entire part, whereas the settings on the ADC A through ADC D tabs each affect

the selected channel only. See the data sheet, the

, High Speed ADC SPI

Control Software, and the

, Interfacing to High Speed ADCs via SPI, for

additional information on the available settings.