Dual, 12-/14-/16-Bit,1 GSPS

Digital-to-Analog Converters

AD9776A/AD9778A/AD9779A

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007–2008 Analog Devices, Inc. All rights reserved.

FEATURES

Low power: 1.0 W @ 1 GSPS, 600 mW @ 500 MSPS,

full operating conditions

Single carrier W-CDMA ACLR = 80 dBc @ 80 MHz IF

Analog output: adjustable 8.7 mA to 31.7 mA,

R

L

= 25 Ω to 50 Ω

Novel 2×, 4×, and 8× interpolator/coarse complex modulator

allows carrier placement anywhere in DAC bandwidth

Auxiliary DACs allow control of external VGA and offset control

Multiple chip synchronization interface

High performance, low noise PLL clock multiplier

Digital inverse sinc filter

100-lead, exposed paddle TQFP

APPLICATIONS

Wireless infrastructure

W-CDMA, CDMA2000, TD-SCDMA, WiMax, GSM, LTE

Digital high or low IF synthesis

Internal digital upconversion capability

Transmit diversity

Wideband communications: LMDS/MMDS, point-to-point

GENERAL DESCRIPTION

The AD9776A/AD9778A/AD9779A are dual, 12-/14-/16-bit,

high dynamic range digital-to-analog converters (DACs) that

provide a sample rate of 1 GSPS, permitting a multicarrier

generation up to the Nyquist frequency. They include features

optimized for direct conversion transmission applications,

including complex digital modulation and gain and offset

compensation. The DAC outputs are optimized to interface

seamlessly with analog quadrature modulators such as the

ADL537x FMOD series from Analog Devices, Inc. A 3-wire

interface provides for programming/readback of many internal

parameters. Full-scale output current can be programmed over

a range of 10 mA to 30 mA. The devices are manufactured on

an advanced 0.18 μm CMOS process and operate on 1.8 V and

3.3 V supplies for a total power consumption of 1.0 W. They are

enclosed in a 100-lead thin quad flat package (TQFP).

PRODUCT HIGHLIGHTS

1.

Ultralow noise and intermodulation distortion (IMD)

enable high quality synthesis of wideband signals from

baseband to high intermediate frequencies.

2.

A proprietary DAC output switching technique enhances

dynamic performance.

3.

The current outputs are easily configured for various

single-ended or differential circuit topologies.

4.

CMOS data input interface with adjustable setup and hold.

5.

Novel 2×, 4×, and 8× interpolator/coarse complex

modulator allows carrier placement anywhere in DAC

bandwidth.

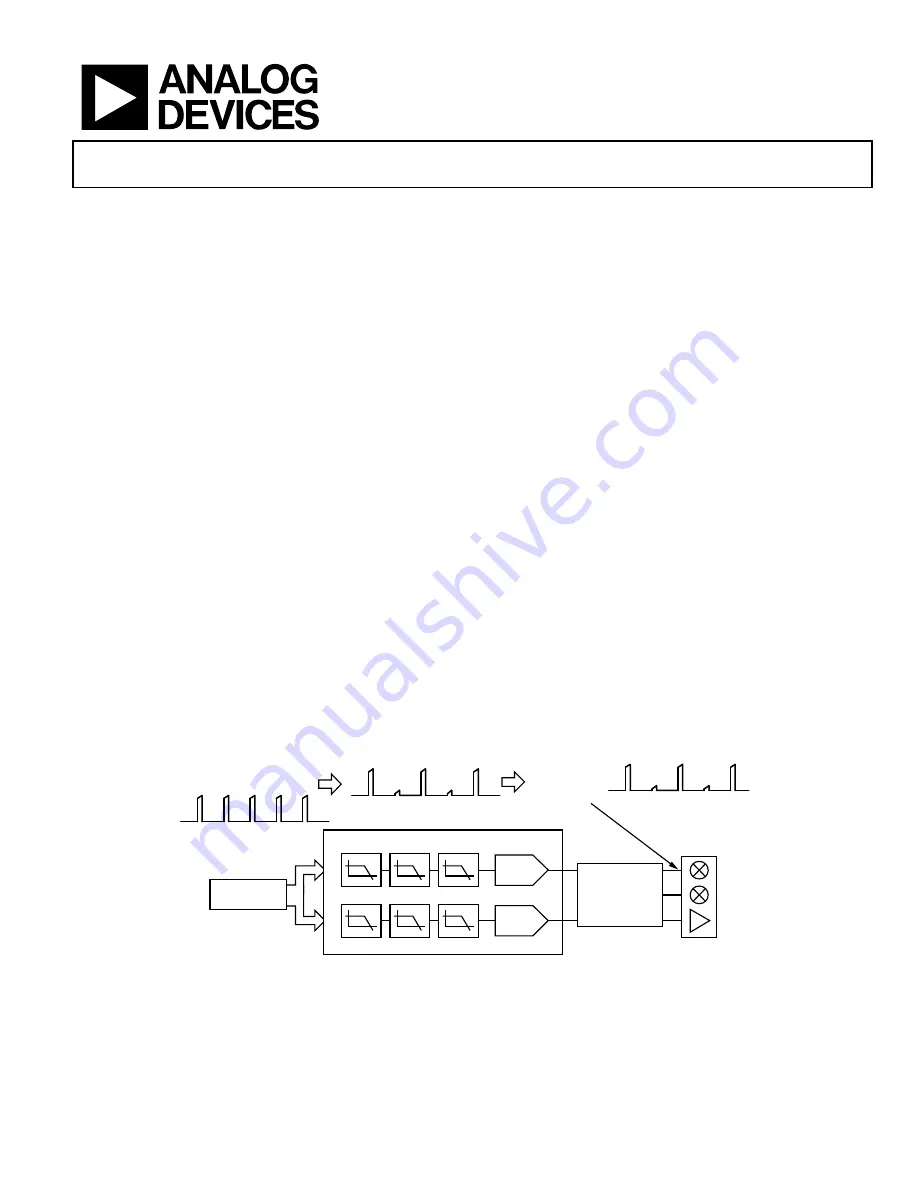

TYPICAL SIGNAL CHAIN

FPGA/ASIC/DSP

DC

COMPLEX I AND Q

DC

LO

QUADRATURE

MODULATOR/

MIXER/

AMPLIFIER

I DAC

Q DAC

DIGITAL INTERPOLATION FILTERS

AD9776A/AD9778A/AD9779A

POST DAC

ANALOG FILTER

A

0

64

52

-114

Figure 1.