AD9776A/AD9778A/AD9779A

Rev. B | Page 44 of 56

GAIN AND OFFSET CORRECTION

Analog quadrature modulators make it very easy to realize

single sideband radios. However, there are several nonideal

aspects of quadrature modulator performance. Among these

analog degradations are

•

Gain mismatch: The gain in the real and imaginary signal

paths of the quadrature modulator may not be matched

perfectly. This leads to less than optimal image rejection

because the cancellation of the negative frequency image is

less than perfect.

•

Local oscillator (LO) feedthrough: The quadrature mod-

ulator has a finite dc-referred offset, as well as coupling

from its LO port to the signal inputs. These can lead to

significant spectral spurs at the frequency of the quadrature

modulator LO.

The AD9776A/AD9778A/AD9779A have the capability to

correct for both of these analog degradations. Note that these

degradations drift over temperature; therefore, if close to optimal

single sideband performance is desired, a scheme for sensing

these degradations over temperature and correcting for them

may be necessary.

I/Q CHANNEL GAIN MATCHING

Gain matching is achieved by adjusting the values in the DAC

gain registers. For the I DAC, these values are in the 0x0B and

0x0C I DAC control registers. For the Q DAC, these values are

in the 0x0F and 0x10 Q DAC control registers. These are 10-bit

values. To perform gain compensation, raise or lower the value

of one of these registers by a fixed step size and measure the

amplitude of the unwanted image. If the unwanted image is

increasing in amplitude, stop the procedure and try the same

adjustment on the other DAC control register. Do this until the

image rejection cannot be improved through further adjustment

of these registers.

It should be noted that LO feedthrough compensation is inde-

pendent of gain. However, gain compensation can affect the LO

compensation because the gain compensation may change the

common-mode level of the signal. The dc offset of some

modulators is common-mode level dependent. Therefore, it is

recommended that the gain adjustment be performed prior to

LO compensation.

AUXILIARY DAC OPERATION

Two auxiliary DACs are provided on the AD9776A/AD9778A/

AD9779A. The full-scale output current on these DACs is derived

from the 1.2 V band gap reference and external resistor between

the I120 pin and ground. The gain scale from the reference

amplifier current (I

REFERENCE

) to the auxiliary DAC reference

current is 16.67 mA with the auxiliary DAC gain set to full

scale (10-bit values, 3-wire interface Register 0x0D and 3-wire

interface Register 0x11). This results in a full-scale current of

approximately 2 mA for auxiliary DAC1 and auxiliary DAC2.

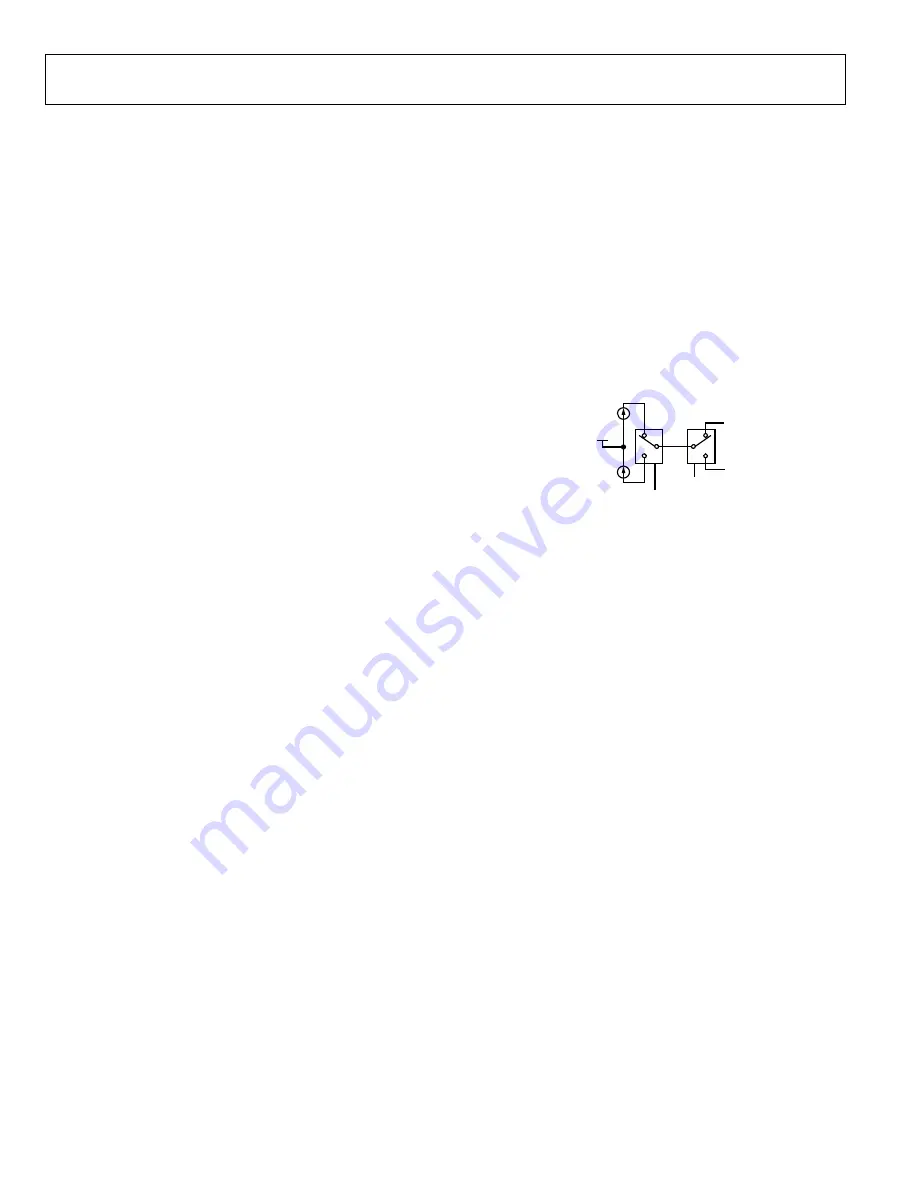

The auxiliary DAC structure is shown in Figure 78. Only one of

the two output pins of the auxiliary DAC is active at a time. The

inactive side goes to a high impedance state (>100 kΩ). The

active output pin is chosen by writing to Bit 7 of Register 0x0E

and Register 0x12.

The active output can act as either a current source or a current

sink. When sourcing current, the output compliance voltage is

0 V to 1.6 V. When sinking current, the output compliance voltage

is 0.8 V to 1.6 V. The output pin is chosen to be a current source or

current sink by writing to Bit 6 of Register 0x0E and Register 0x12.

0

645

2-

3

03

AUXP

AUXN

P/N

SOURCE/

SINC

0mA TO 2mA

(SOURCE)

V

BIAS

0mA TO 2mA

(SINK)

Figure 78. Auxiliary DAC Source/Sink for AD9776A/AD9778A/AD97779A

The magnitude of the auxiliary DAC1 current is controlled by the

0x0D and 0x0E auxiliary DAC1 control registers; the magnitude of

the auxiliary DAC2 current is controlled by the 0x11 and 0x12

auxiliary DAC2 control registers. These auxiliary DACs have

the ability to source or sink current. This is programmable via

Bit 6 in either auxiliary DAC control register. The choice of

sinking or sourcing should be made at circuit design time.

There is no advantage to switching between current source or

current sink once the circuit is in place.

The auxiliary DACs can be used for LO cancellation when the

DAC output is followed by a quadrature modulator. This LO

feedthrough is caused by the input-referred dc offset voltage of

the quadrature modulator (and the DAC output offset voltage

mismatch) and may degrade system performance.

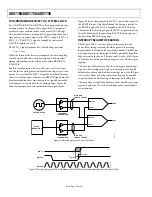

Typical DAC-to-quadrature modulator interfaces are shown

in Figure 79. Often, the input common-mode voltage for the

modulator is much higher than the output compliance range of

the DAC, making ac coupling or a dc level shift necessary. If the

required common-mode input voltage on the quadrature modu-

lator matches that of the DAC, then the dc shown in Figure 79 can

be used. A low-pass or band-pass passive filter is recommended

when spurious signals from the DAC (distortion and DAC images)

at the quadrature modulator inputs may affect the system perfor-

mance. Placing the filter at the location shown in Figure 79 allows

easy design of the filter because the source and load impedances

can easily be designed close to 50 Ω.