AD9776A/AD9778A/AD9779A

Rev. B | Page 52 of 56

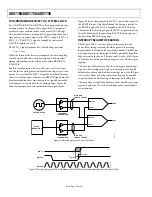

0

0

250

f

DATA

(MSPS)

PO

W

E

R

(W

)

0.125

25

50

75

100

125

150

175

200

225

2× INTERPOLATION

4× INTERPOLATION

1× INTERPOLATION,

NO MODULATION

8× INTERPOLATION, f

DAC

/8,

f

DAC

/4,

f

DAC

/2,

NO MODULATION

0.100

0.075

0.050

0.025

06

45

2-

0

82

Figure 97. Power Dissipation, Clock 1.8 V Supply, I and Q Data, Dual DAC

Mode, Does Not Include Zero Stuffing

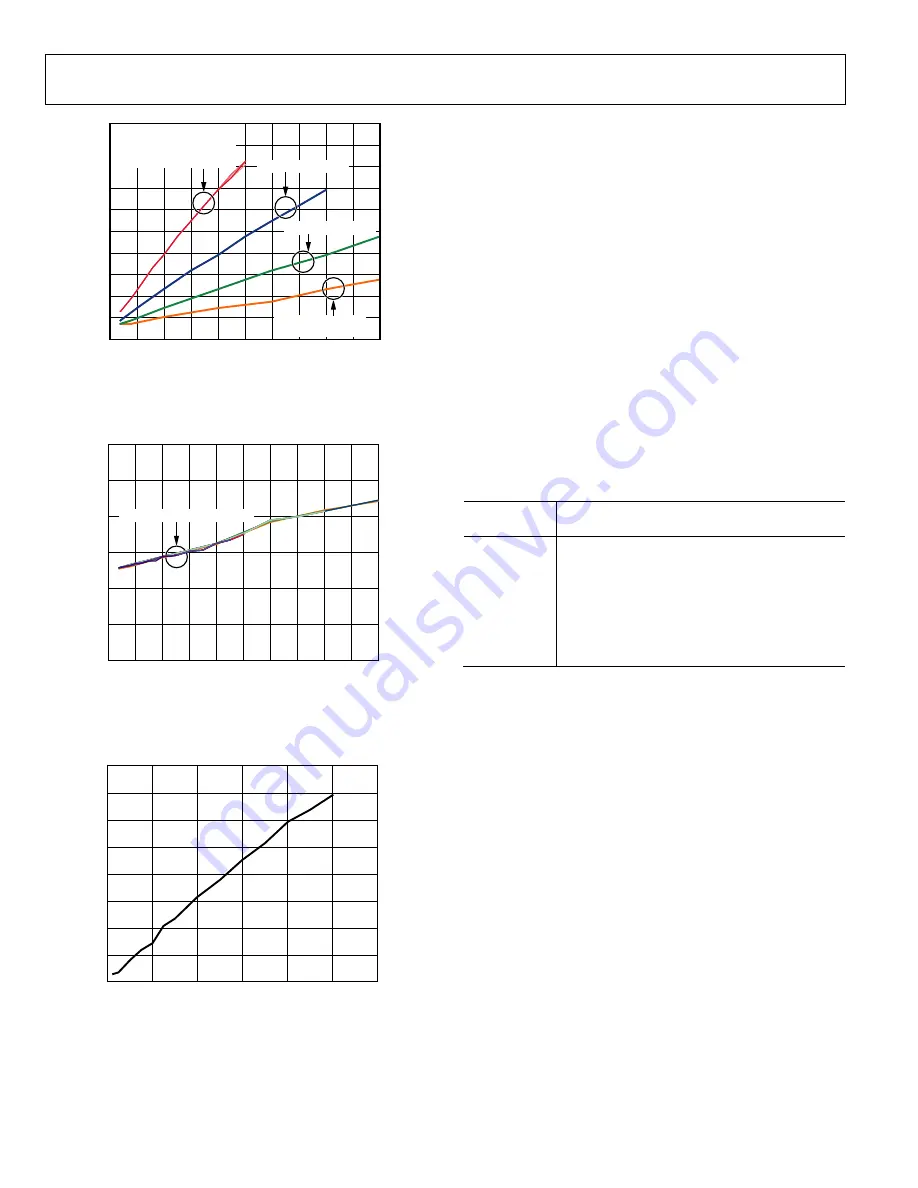

0

0

250

f

DATA

(MSPS)

PO

W

E

R

(

W

)

0.075

25

50

75

100

125

150

175

200

225

0.050

0.025

ALL INTERPOLATION MODES

06

45

2-

0

83

Figure 98. Power Dissipation, Digital 3.3 V Supply, I and Q Data,

Dual DAC Mode

0.16

0

0

1200

f

DAC

(MSPS)

PO

W

E

R

(

W

)

0.14

0.12

0.10

0.08

0.06

0.04

0.02

200

400

600

800

1000

06

45

2-

0

84

Figure 99. DVDD18 Power Dissipation of Inverse Sinc Filter

POWER-DOWN AND SLEEP MODES

The AD9776A/AD9778A/AD9779A have a variety of power-down

modes; thus, the digital engine, main TxDACs, or auxiliary DACs

can be powered down individually or together. Via the 3-wire

interface port, the main TxDACs can be placed in sleep or power-

down mode. In sleep mode, the TxDAC output is turned off,

thus reducing power dissipation. The reference remains powered

on, however, so that recovery from sleep mode is very fast. With

the power-down mode bit set (Register 0x00, Bit 4), all analog

and digital circuitry, including the reference, is powered down.

The 3-wire interface port remains active in this mode. This

mode offers more substantial power savings than sleep mode,

but the turn-on time is much longer. The auxiliary DACs also

have the capability to be programmed into sleep mode via the

3-wire interface port. The auto power-down enable bit (Register

0x00, Bit 3) controls the power-down function for the digital

section of the devices. The auto power-down function works in

conjunction with the TXENABLE pin (Pin 39); see Table 31 for

details.

Table 31.

TXENABLE

(Pin 39)

Description

0

If auto power-down enable bit = 0, flush data

path with 0s.

If auto power-down enable bit = 1, flush data for

multiple REFCLK cycles; then, automatically

place the digital engine in power-down state.

DACs, reference, and 3-wire interface port are

not affected.

1 Normal

operation.