AD9776A/AD9778A/AD9779A

Rev. B | Page 49 of 56

DEVICE SYNCHRONIZATION

System demands can impose two different requirements for

synchronization. Some systems require multiple DACs to be

synchronized to each other. This is the case when supporting

transmit diversity or beam forming, where multiple antennas

are used to transmit a correlated signal. In this case, the DAC

outputs need to be phase aligned with each other, but there may

not be a requirement for the DAC outputs to be aligned with a

system level reference clock. In systems with a time division

multiplexing transmit chain, one or more DACs may need to be

synchronized with a system level reference clock. The options

for synchronizing devices under these two conditions are

described in the Synchronization Logic Overview section

and the Synchronizing Devices to a System Clock section.

SYNCHRONIZATION LOGIC OVERVIEW

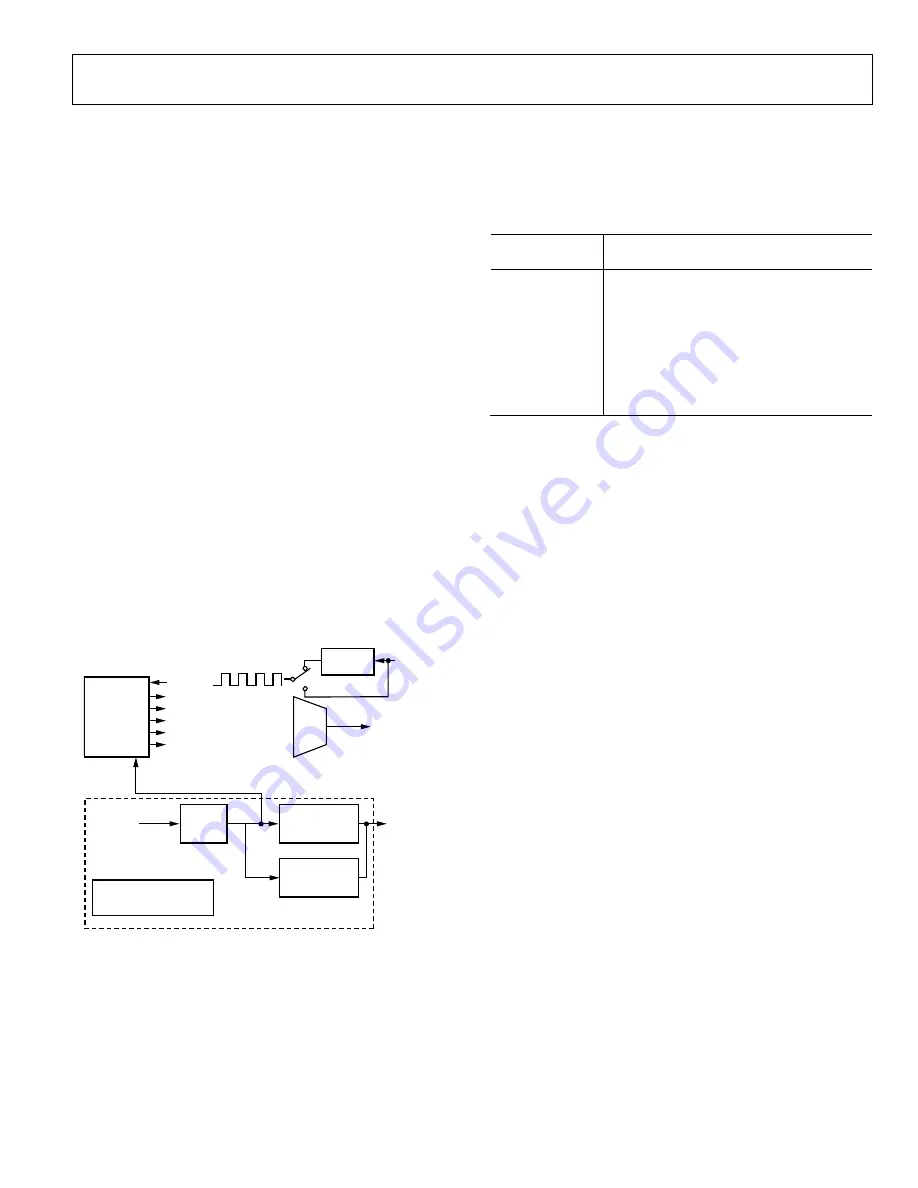

Figure 88 shows the block diagram of the on-chip synchroniza-

tion logic. The basic operation of the synchronization logic is to

generate a single DACCLK-cycle-wide initialization pulse that

sets the clock generation state machine logic to a known state.

This initialization pulse loads the clock generation state machine

with the Clock State[4:0] value as its next state. If the initializa-

tion pulse from the synchronization logic is generated properly,

it is active for one DACCLK cycle, every 32 DACCLK cycles.

Because the clock generation state machine has 32 states operating

at the DACCLK rate, every initialization pulse received after the

first pulse loads the state in which the state machine is already

in, maintaining proper clocking operation of the device.

SYNC

DELAY

PULSE

GENERATION

LOGIC

ERROR DETECT

CIRCUITRY

CLOCK

GENERATION

STATE

MACHINE

DACCLK

BIT 0 (1× INTERPOLATION)

BIT 1 (2×)

BIT 2 (4×)

BIT 3 (8×)

BIT 4 (8× WITH

ZERO STUFFING)

MUX

SYNC IRQ

SYNC_I

DELAY REGISTER

(REG 0x0, BITS

[

7:4

])

REFCLK

INTERNAL

PLL

PLL

BYPASS

06

45

2-

0

94

LOAD DACCLK OFFSET VALUE (REG 0x07,

BITS[4:0]), ONE DACCLK CYCLE/INCREMENT

f

SYNC_1

<

f

DATA

/2^N

Figure 88. Synchronization Circuitry Block Diagram

Nominally, the SYNC_I input should have one rising edge every

32 clock cycles (or multiple of 32 clock cycles) to maintain

proper synchronization. The pulse generation logic can be

programmed to suppress outgoing pulses if the incoming

SYNC_I frequency is greater than DACCLK/32. Extra pulses

can be suppressed by the ratios listed in Table 30. The SYNC_I

frequency can be lower than DACCLK/32 as long as output

pulses are generated from the pulse generation circuit on a

multiple of 32 DACCLK periods. In any case, the maximum

frequency of SYNC_I must be less than f

DATACLK

.

Table 30. Settings Required to Support Various SYNC_I

Frequencies

SYNC_I

Ratio[2:0]

SYNC_I Rising Edges Required for

Synchronization Pulse

000 1

(default)

001 2

010 4

011 8

100 16

101 Invalid

setting

110 Invalid

setting

111 Invalid

setting

As an example, if a SYNC_I signal with a frequency of f

DACCLK

/4

is used, then both 011 and 100 are valid settings for the SYNC_I

Ratio[2:0] value. A setting of 011 results in one initialization

pulse being generated every 32 DACCLK cycles, and a setting

of 100 results in one initialization pulse being generated every

64 DACCLK cycles. Both cases result in proper device

synchronization.

The Clock State[4:0] value is the state to which the clock

generation state machine resets upon initialization. By varying

this value, the timing of the internal clocks with respect to the

SYNC_I signal can be adjusted. Every increment of the Clock

State[4:0] value advances the internal clocks by one DACCLK

period.

Synchronization Timing Error Detection

The synchronization logic has error detection circuitry similar to

the input data timing. The SYNC_I Timing Margin[3:0] variable

determines how much setup and hold margin the synchronization

interface needs for the sync timing error IRQ bit to remain inactive

(that is, to indicate error free operation). Therefore, the sync timing

error IRQ bit is set whenever the setup and hold margins drop

below the SYNC_I Timing Margin[3:0] value and, therefore,

does not necessarily indicate that the SYNC_I input was latched

incorrectly.

When the sync timing error IRQ bit is set, corrective action can

be taken to restore timing margin. One course of action is to

temporarily reduce the timing margin until the sync timing

error IRQ is cleared. Then, increase the SYNC_I delay by two

increments and check whether the timing margin has increased

or decreased. If it has increased, continue incrementing the

value of SYNC_I delay until the margin is maximized. However,

if incrementing the SYNC_I delay reduced the timing margin,

then the delay should be reduced until the timing margin is

optimized.