AD9779

Preliminary Technical Data

Rev. PrD | Page 14 of 34

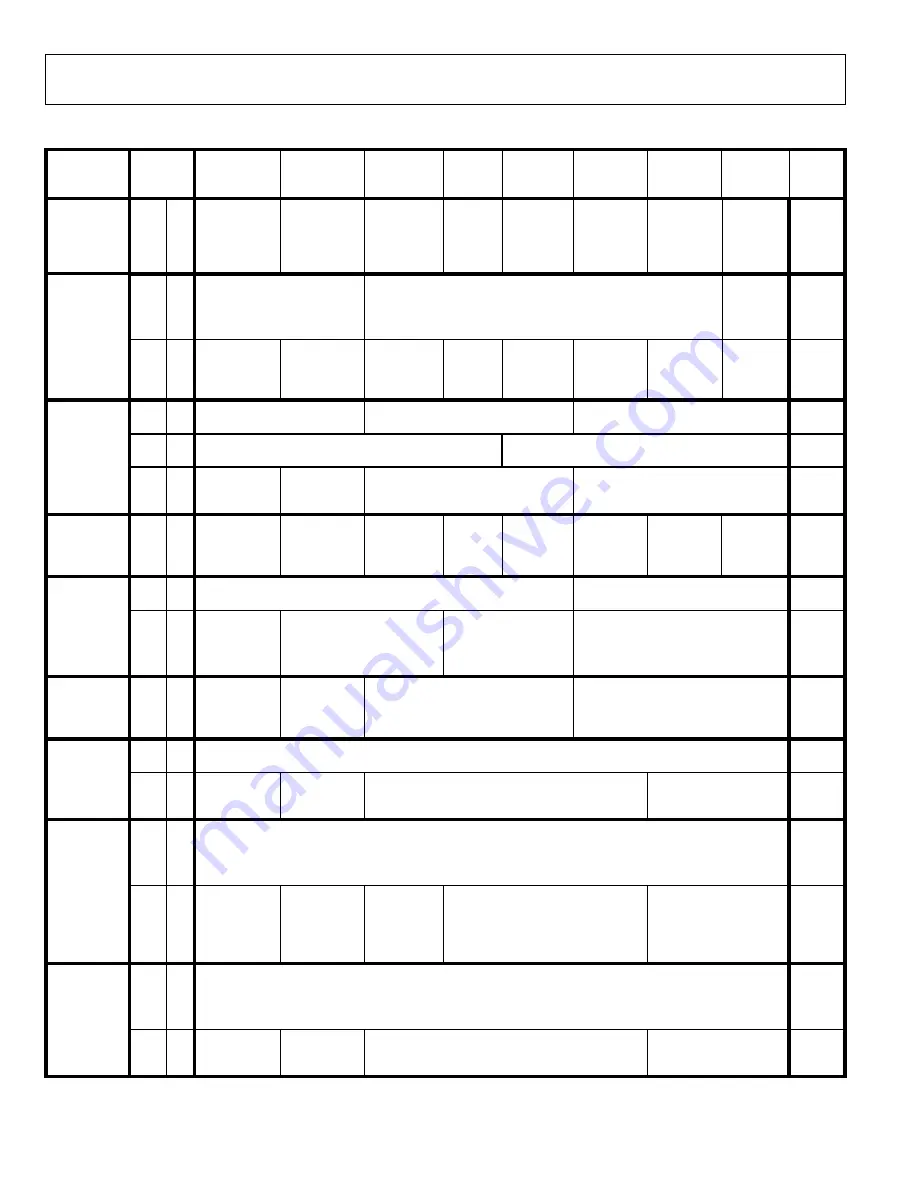

SPI Register Map

Register

Name

Address

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Default

Comm

Register

00h 00 SDIO

Bidirectional

LSB,MSB First

Software

Reset

Power

Down

Mode

Auto

Power

Down

Enable

PLL Lock

Indicator

00h

01h

01

Filter Interpolation Factor

<1: 0>

Filter Interpolation Mode <4:0>

Zero

Stuffing

Enable

00h

Digital

Control

Register

02h

02

Data Format

One Port

Mode

Real Mode

Inverse

Sinc

Enable

DATACLK

Invert

IQ Select

Invert

Q First

00h

03h

03

Data Delay Mode <1:0>

Data Clock Delay <2:0>

Data Window Delay <2:0>

00h

04h

04

Sync Out Delay <3:0>

Sync Window Delay <3:0>

00h

Sync

Control

05h 05 Sync

Enable

Sync Driver

Enable

Dac Clock Offset <2:0>

00h

Interrupt

Register

06h 06 Data

Delay

IRQ

Sync Delay

IRQ

Cross

Control IRQ

Data

Delay

IRQ Enable

Sync Delay

IRQ Enable

Cross

Control IRQ

Enable

00h

07h

07

PLL Band Select <4:0>

PLL Loop Cap Select <2:0>

CFh

PLL Control

08h

08

PLL Enable

PLL Output Freq Divide

<1:0>

PLL Loop Freq Divide

<1:0>

PLL Loop Filter Pole/Zero <2:0>

37h

Misc.

Control

Register

09h 24 PLL

Error

Source

PLL Ref

Bypass

PLL Gain <2:0>

PLL Bias <2:0>

38h

0Ah

09

IDAC Gain Adjustment <7:0>

F9h

I DAC

Control

Register

0Bh

10

IDAC SLEEP

IDAC Power

Down

IDAC

Gain

Adjustment

<9:8>

01h

0Ch

11

Auxiliary DAC1 Data <7:0>

00h

Aux 1 DAC

Control

Register

0Dh 12 Auxiliary

DAC1 Sign

Auxiliary

DAC1

Current

Direction

Auxiliary

DAC1 Sleep

Auxiliary DAC1 Data

<9:8>

00h

0Eh

13

QDAC Gain Adjustment <7;0>

F9h

Q DAC

Control

Register

0Fh

14

QDAC SLEEP

QDAC Sleep

QDAC Gain Adjustment

<9:8>

01h