Preliminary Technical Data

AD9779

Rev. PrD | Page 15 of 34

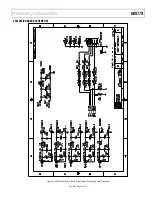

10h

15

Auxiliary DAC2 Data <7:0>

00h

Aux 2 DAC

Control

Register

11h 16 Auxiliary

DAC2 Sign

Auxiliary

DAC2

Current

Direction

Auxiliary

DAC2 Power

Down

Auxiliary DAC2 Data

<9:8>

00h

12h 17 Cross

Updel

<7:0>

00h

13h 18 Cross

Dndel

<7:0>

00h

14h

19

Cross Clock Divide <3:0>

Cross Wiggle Delay <3:0>

00h

Cross

Register

15h 20 Cross

Run

Cross Status

Cross Done

Cross Wiggle <2:0>

Cross Step <1:0>

00h

Analog

Write

16h 23 Analog

Write

<7:0>

00h

17h

21

Mirror Roll Off <1:0>

Band Gap Trim <2:0>

00h

Analog

Control

Register

18h

22

Stack Headroom Control<7:0>

CAh

Analog

Status

Register

19h 25

Analog Status <7:0>

--h

Test 1

Register

1Ah

26

MISR Enable

MISR IQ

Select

MISR

Samples

Internal

Data

Enable

Test Mode <2:0>

00h

1Bh 27

BIST<31:24>

--h

1Ch 28

BIST<23:16>

--h

1Dh 29

BIST<15:8>

--h

Test 2

Register

1Eh 30

BIST<7:0>

--h

Table 11

:

SPI Register Map