AD9779

Preliminary Technical Data

Rev. PrD | Page 34 of 34

ESD CAUTION

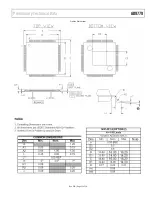

ORDERING GUIDE

Table 15: Ordering Guide

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features proprietary

ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges.

Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Model Temperature

Range

Description

AD9779BSV

-40

°

C to +85

°

C (Ambient)

100-Lead TQFP, Exposed Paddle

AD9779/PCB

25°C (Ambient)

Evaluation Board

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

PR05363–0–1/05(PrD)