Preliminary Technical Data

AD9779

Rev. PrD | Page 5 of 34

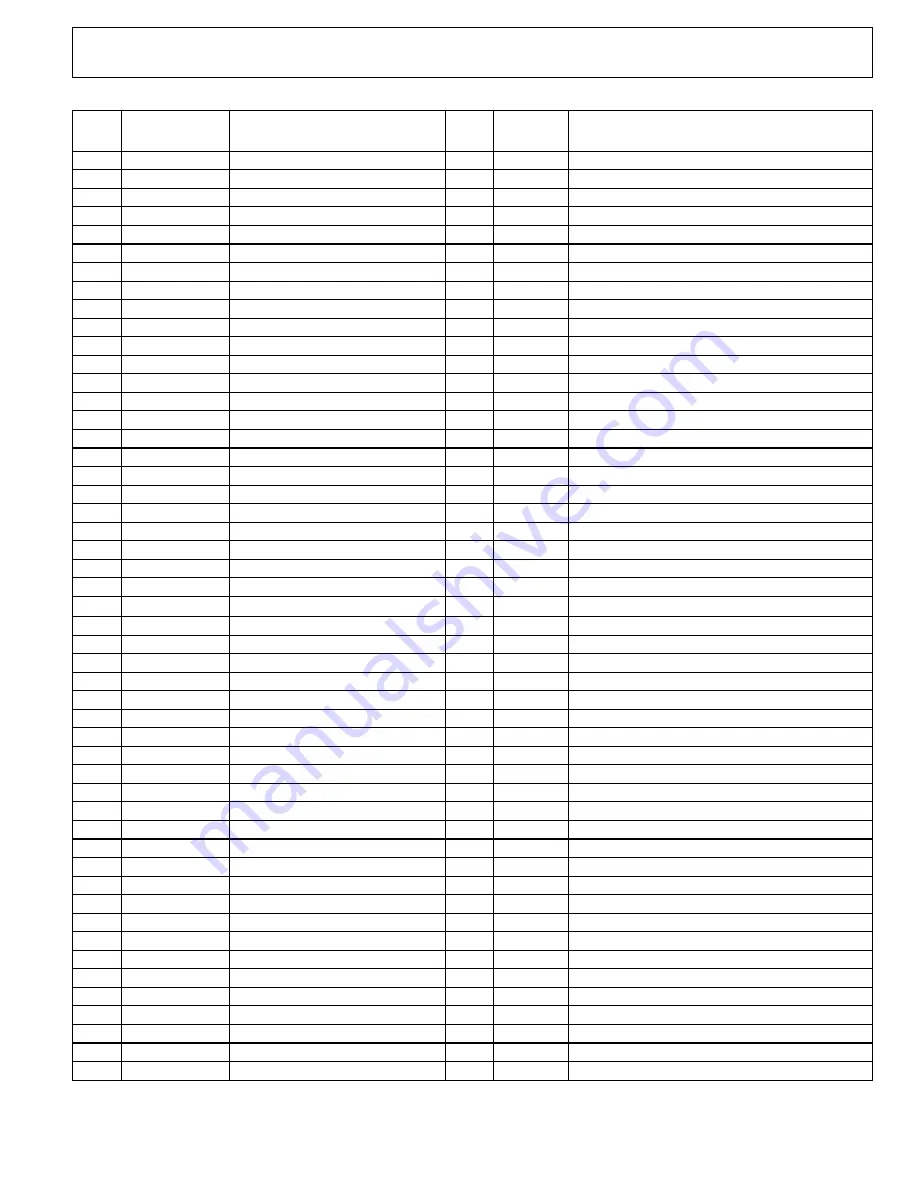

PIN FUNCTION DESCRIPTIONS

Pin

No.

Name Description

Pin

No.

Name Description

1

VDDC18

1.8 V Clock Supply

51

P2D<6>

Port 2 Data Input D6

2

VDDC18

1.8 V Clock Supply

52

P2D<5>

Port 2 Data Input D5

3

VSSC

Clock Common

53

VDDD18

1.8 V Digital Supply

4

VSSC

Clock Common

54

VSSD

Digital Common

5

CLK+

Differential Clock Input

55

P1D<4>

Port 2 Data Input D4

6

CLK-

Differential Clock Input

56

P1D<3>

Port 2 Data Input D3

7

VSSC

Clock Common

57

P1D<2>

Port 2 Data Input D2

8

VSSC

Clock Common

58

P1D<1>

Port 2 Data Input D1

9

VDDC18

1.8 V Clock Supply

59

P1D<0>

Port 2 Data Input D0 (LSB)

10

VDDC18

1.8 V Clock Supply

60

VDDD18

1.8 V Digital Supply

11

VSSC

Clock Common

61

VDDD33

3.3 V Digital Supply

12 VSSC

Clock

Common

62

SYNC_O-

Differential Synchronization Output

13

Differential Synchronization Input

63

Differential

Synchronization

Output

14 SYNC_I-

Differential

Synchronization Input

64

VSSD

Digital Common

15

VSSD

Digital Common

65

PLL_LOCK

PLL Lock Indicator

16

VDDD33

3.3 V Digital Supply

66

SPI_SDO

SPI Port Data Output

17

P1D<15>

Port 1 Data Input D15 (MSB)

67

SPI_SDIO

SPI Port Data Input/Output

18

P1D<14>

Port 1 Data Input D14

68

SPI_CLK

SPI Port Clock

19

P1D<13>

Port 1 Data Input D13

69

SPI_CSB

SPI Port Chip Select Bar

20

P1D<12>

Port 1 Data Input D12

70

RESET

Reset

21

P1D<11>

Port 1 Data Input D11 71

IRQ

Interrupt

Request

22

VSSD

Digital Common

72

VSS

Analog Common

23

VDDD18

1.8 V Digital Supply

73

IPTAT

Reference Current

24

P1D<10>

Port 1 Data Input D10

74

VREF

Voltage Reference Output

25

P1D<9>

Port 1 Data Input D9

75

I120

120

µ

A Reference Current

26

P1D<8>

Port 1 Data Input D8

76

VDDA33

3.3 V Analog Supply

27

P1D<7>

Port 1 Data Input D7

77

VSSA

Analog Common

28

P1D<6>

Port 1 Data Input D6

78

VDDA33

3.3 V Analog Supply

29

P1D<5>

Port 1 Data Input D5

79

VSSA

Analog Common

30

P1D<4>

Port 1 Data Input D4

80

VDDA33

3.3 V Analog Supply

31

P1D<3>

Port 1 Data Input D3

81

VSSA

Analog Common

32

VSSD

Digital Common

82

VSSA

Analog Common

33

VDDD18

1.8 V Digital Supply

83

IOUT2_P

Differential DAC Current Output, Channel 2

34

P1D<2>

Port 1 Data Input D2

84

IOUT2_N

Differential DAC Current Output, Channel 2

35

P1D<1>

Port 1 Data Input D1

85

VSSA

Analog Common

36

P1D<0>

Port 1 Data Input D0 (LSB)

86

AUX2_P

Auxiliary DAC Voltage Output, Channel 2

37

DATACLK_OUT

Data Clock Output

87

AUX2_N

Auxiliary DAC Voltage Output, Channel 2

38

VDDD33

3.3 V Digital Supply

88

VSSA

Analog Common

39 TXENABLE

Transmit

Enable

89

AUX1_N

Auxiliary DAC Voltage Output, Channel 1

40

P2D<15>

Port 2 Data Input D15 (MSB)

90

AUX1_P

Auxiliary DAC Voltage Output, Channel 1

41

P2D<14>

Port 2 Data Input D14

91

VSSA

Analog Common

42

P2D<13>

Port 2 Data Input D13

92

IOUT1_N

Differential DAC Current Output, Channel 1

43

VDDD18

1.8 V Digital Supply

93

IOUT1_P

Differential DAC Current Output, Channel 1

44

VSSD

Digital Common

94

VSSA

Analog Common

45

P2D<12>

Port 2 Data Input D12

95

VSSA

Analog Common

46

P2D<11>

Port 2 Data Input D11

96

VDDA33

3.3 V Analog Supply

47

P2D<10>

Port 2 Data Input D10

97

VSSA

Analog Common

48

P2D<9>

Port 2 Data Input D9

98

VDDA33

3.3 V Analog Supply

49

P2D<8>

Port 2 Data Input D8

99

VSSA

Analog Common

50

P2D<7>

Port 2 Data Input D7

100

VDDA33

3.3 V Analog Supply

Table 4: Pin Function Descriptions