ADM1060

Rev. B | Page 12 of 52

where

Voltage Range

V

B

(V)

V

R

(V)

0.6 V to 1.8 V

0.604

1.204

1 V to 3 V

1.003

1.999

2 V to 6 V

2.005

3.997

4.8 V to 14.4 V

4.849

9.666

–2 V to –6 V

–1.994

–3.995

V

T

is the desired threshold voltage (UV or OV)

V

R

is the threshold voltage range

N

is the decimal value of the 8 bit code

V

B

is the bottom of threshold range

The code for a given threshold is therefore given by

N

= 255 × (

V

T

–

V

B

)/V

R

For example, if the user wishes to set a 5 V OV threshold on

VP1, the code to be programmed in the PS1OVTH register

(discussed later) would be

N

= 255 × (5 – 2.005)/3.997

Thus,

N

= 191 (1011 1111 binary, or 0xBF)

The available threshold ranges and their resolutions are shown

in Table 3. Note that the low end of the detection range is fixed

at 33.33% of the top of the range. Note also that for a given SFD,

the ranges overlap; for example, VH goes from 2 V to 6 V and

then from 4.8 V to 14.4 V. This is to provide better threshold

setting resolution as supplies decrease in value.

Table 3. Input Threshold Ranges and Resolution

Input Name

Voltage Ranges

Resolution

4.8 V to 14.4 V

37.6 mV

VH

2 V to 6 V

15.6 mV

2 V to 6 V

15.6 mV (Pos. Mode)

1 V to 3 V

7.8 mV (Pos. Mode)

VBn

−6 V to −2 V

15.6 mV (Neg. Mode)

2 V to 6 V

15.6 mV

1 V to 3 V

7.8 mV

VPn

0.6 V to 1.8 V

4.7 mV

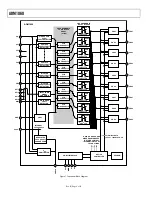

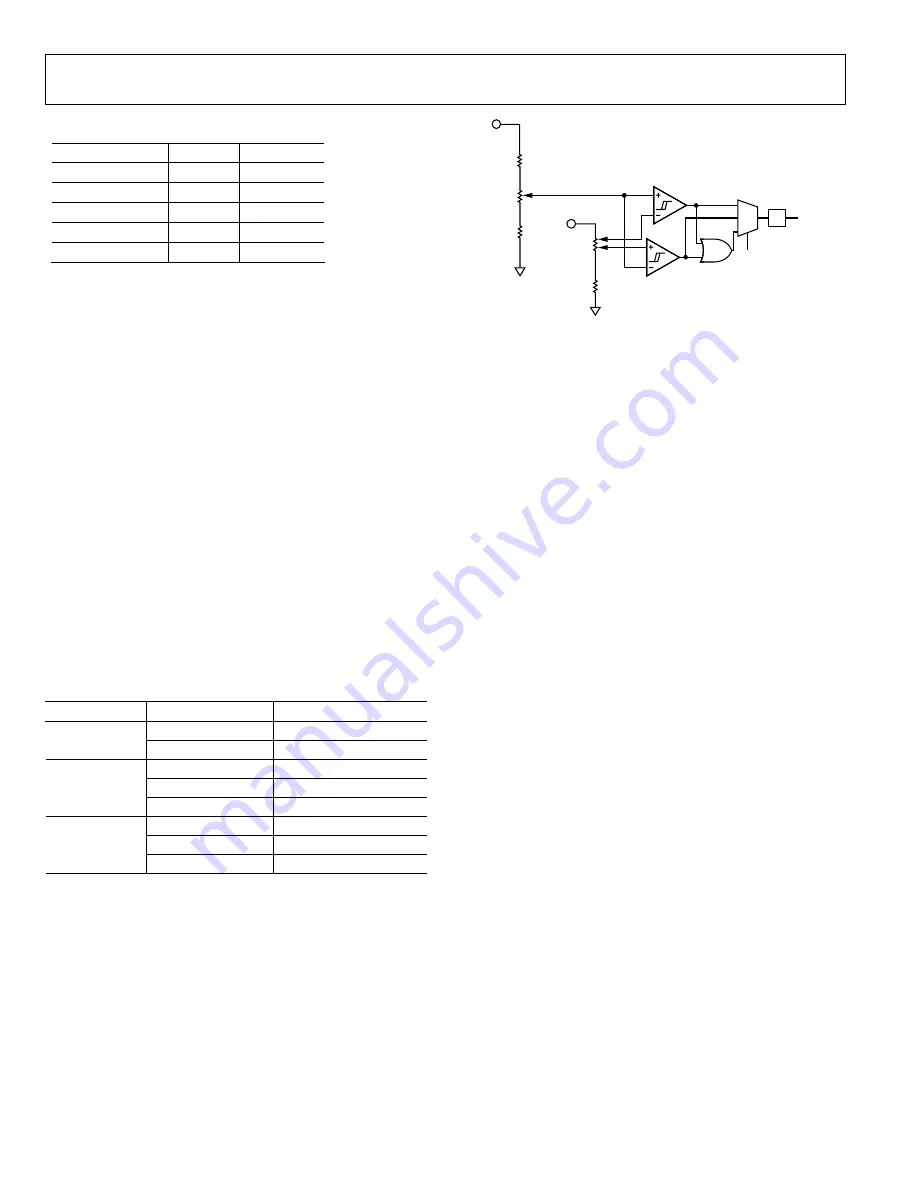

Figure 18 illustrates the function of the programmable SFD (for

the case of a positive supply).

RANGE SELECT

DAC (1 OR 2 BITS)

VREF

UV

COMPARATOR

OV

COMPARATOR

FAULT TYPE

SELECT

GLITCH

FILTER

DUAL 8-BIT

DAC FOR

SETTING UV

AND OV

THRESHOLDS

FAULT

OUTPUT

VPn

Figure 18. Positive Programmable Supply Fault Detector

SFD COMPARATOR HYSTERESIS

The OV and UV comparators shown in Figure 18 are always

looking at VPn via a potential divider. In order to avoid

chattering (multiple transitions when the input is very close to

the set threshold level), these comparators have digitally

programmable hysteresis. The UV and OV hysteresis can be

programmed in two registers that are similar but separate to the

UV or OV threshold registers. Only the five LSBs of these

registers can be set. The hysteresis is added after the supply

voltage goes out of tolerance. Thus, the user can determine how

much above the UV threshold the input must rise again before a

UV fault is deasserted. Similarly, the user can determine how

much below the OV threshold the input must fall again before

an OV fault is deasserted. The hysteresis figure is given by

V

H

=

V

R

×

N

THRESH

/255

where

V

H

is the desired hysteresis voltage

N

THRESH

is the decimal value of the 5-bit hysteresis code

Therefore, if the low range threshold detector was selected, the

max hysteresis is defined as

(3 V – 1 V) × 31/255 = 242 mV, where (2

5

– 1 = 31)

The hysteresis programming resolution is the same as the

threshold detect ranges—that is, 37.5 mV on the high range,

15.6 mV on the midrange, 7.8 mV on the low range, and 4.7 mV

on the ultralow range.

BIPOLAR SFDs

The two bipolar SFDs also allow the detection of faults on nega-

tive supplies. A polarity bit in the setup register for this SFD

(Bit 7 in Register BSnSEL—see register map overleaf) deter-

mines if a positive or negative input should be applied to VBn.

Only one range (−6 V to −2 V) is available when the SFDs are in

negative mode. Note that the bipolar SFDs cannot be used to

power the ADM1060, even if the voltage on VBn is positive.