ADM1060

Rev. B | Page 17 of 52

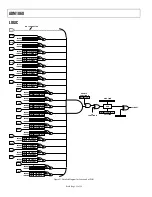

POSITIVE VOLTAGE SUPPLY FAULT DETECT (PSn SFD) REGISTERS

Table 15. Register 0xB8, 0xC0, 0xC8, 0xD0 PSnOVTH

(Power-On Default 0xFF)

Bit Name

R/W Description

7−0 OV7−OV0 R/W 8-Bit Digital Value for OV Thresh-

old on PSn SFD.

Table 16. Register 0xB9, 0xC1, 0xC9, 0xD1 PSnOVHYST

(Power-On Default 0x00)

Bit Name

R/W Description

7–5

Reserved

N/A

Cannot Be Used

4−0 HY4−HY0 R/W 5-Bit Digital Value for Hysteresis

on OV Threshold of PSn SFD

Table 17. Register 0xBA, 0xC2, 0xCA, 0xD2 PSnUVTH

(Power-On Default 0x00)

Bit Name

W Description

7−0 UV7−UV0 R/W 8-Bit Digital Value for UV Thresh-

old on PSn SFD

Table 18. Register 0xBB, 0xC3, 0xCB, 0xD3 PSnUVHYST

(Power-On Default 0x00)

Bit Name

W Description

7−5

Reserved

N/A

Cannot Be Used

4−0 HY4−HY0 R/W 5-Bit Digital Value for Hysteresis

on UV Threshold of PSn SFD

Table 19. Register 0xBC, 0xC4, 0xCC, 0xD4 PSnSEL (Power-On Default 0x00)

Bit Name

R/W

Description

7

Reserved

N/A

Cannot Be Used

GF2

GF1

GF0

Glitch Filter Delay (µs)

0 0 0

0

0 0 1

5

0 1 0

10

0 1 1

20

1 0 0

30

1 0 1

50

1 1 0

75

6−4 GF2−GF0 R/W

1 1 1

100

RSEL1

RSEL0

Bottom of Range

Top of Range

Step Size (mV)

0

0

2 V

6 V

15.6

0

1

1 V

3 V

7.8

3−2

RSEL1−RESL0

R/W

1

X

0.6 V

1.8 V

4.7

FS1

FS0

Fault Select Type

0 0 Overvoltage

0 1 Undervoltage

1 0 Out-of-Window

1–0 FS1−FS0

R/W

1 1 Not

Allowed