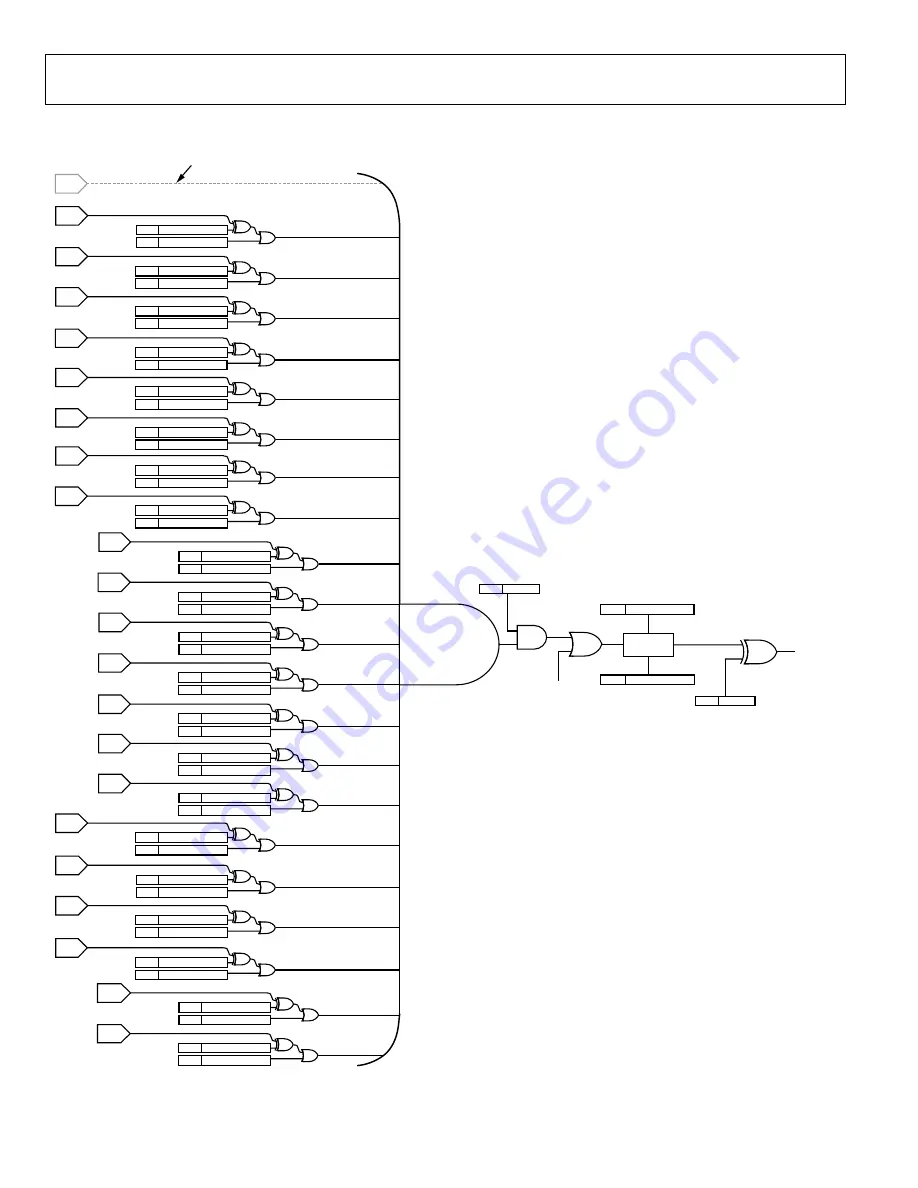

ADM1060

Rev. B | Page 22 of 52

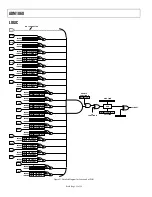

LOGIC

0x00 P1PLBPOLA.0

0x01 P1PLBIMKA.0

INVERT

IGNORE

PLB2

0x00 P1PLBPOLA.1

0x01 P1PLBIMKA.1

INVERT

IGNORE

PLB3

0x00 P1PLBPOLA.2

0x01 P1PLBIMKA.2

INVERT

IGNORE

PLB4

0x00 P1PLBPOLA.3

0x01 P1PLBIMKA.3

INVERT

IGNORE

PLB5

0x00 P1PLBPOLA.4

0x01 P1PLBIMKA.4

INVERT

IGNORE

PLB6

0x00 P1PLBPOLA.5

0x01 P1PLBIMKA.5

INVERT

IGNORE

PLB7

0x00 P1PLBPOLA.6

0x01 P1PLBIMKA.6

INVERT

IGNORE

PLB8

0x00 P1PLBPOLA.7

0x01 P1PLBIMKA.7

INVERT

IGNORE

PLB9

0x02 P1SFDPOLA.0

0x03 P1SFDIMKA.0

INVERT

IGNORE

VB1

0x02 P1SFDPOLA.1

0x03 P1SFDIMKA.1

INVERT

IGNORE

VB2

0x02 P1SFDPOLA.2

0x03 P1SFDIMKA.2

INVERT

IGNORE

VH

0x02 P1SFDPOLA.3

0x03 P1SFDIMKA.3

INVERT

IGNORE

VP1

0x02 P1SFDPOLA.4

0x03 P1SFDIMKA.4

INVERT

IGNORE

VP2

0x02 P1SFDPOLA.5

0x03 P1SFDIMKA.5

INVERT

IGNORE

VP3

0x02 P1SFDPOLA.6

0x03 P1SFDIMKA.6

INVERT

IGNORE

VP4

0x04

P1GPIPOL.4

0x05

P1GPIIMK.4

INVERT

IGNORE

GPI1

0x04

P1GPIPOL.5

0x05

P1GPIIMK.5

INVERT

IGNORE

GPI2

0x04

P1GPIPOL.6

0x05

P1GPIIMK.6

INVERT

IGNORE

GPI3

0x04

P1GPIPOL.7

0x05

P1GPIIMK.7

INVERT

IGNORE

GPI4

0x06

P1WDICFG.7

0x06

P1WDICFG.6

INVERT

IGNORE

WDI_P

0x06

P1WDICFG.5

0x06

P1WDICFG.4

INVERT

IGNORE

WDI_L

0x0C P1PDBTIM.7–4

0x0C P1PDBTIM.3–0

0x07 P1EN.2

0x07 P1EN.1

ENABLE

FUNCTION A

RISE TIME

FALL TIME

PDB

PLBOUT

PLB1

NOT CONNECTED

TO

FUNCTION B

Figure 21. Detailed Diagram for Function A of PLB1