ADSP-2126x SHARC Processor Hardware Reference

10-37

Serial Peripheral Interface Port

SPI Device Select Input Pin

The behavior of the

SPIDS

input depends on the configuration of the SPI.

If the SPI is a slave,

SPIDS

acts as the slave-select input. When enabled as a

master,

SPIDS

can serve as an error-detection input for the SPI in a multi-

master environment. The

ISSEN

bit (bit 4) in the

SPICTL

register enables

the SPI master mode feature. When

ISSEN

=1, the

SPIDS

input is the mas-

ter mode error input; otherwise,

SPIDS

is ignored. The state of these input

pins can be observed in the flag I/O module’s data register.

Buffering and Transmit/Receive Registers

The

TXSPI

and

RXSPI

registers are 32-bit memory-mapped registers that

hold SPI data for transmit and receive operations.

Check the buffer status before reading from or writing to these registers

because the core does not hang when it attempts to read from an empty

buffer or write to a full buffer. When the core writes to a full buffer, the

data in that buffer is overwritten and the SPI begins transmitting the new

data. Invalid data is obtained when the core reads from an empty buffer.

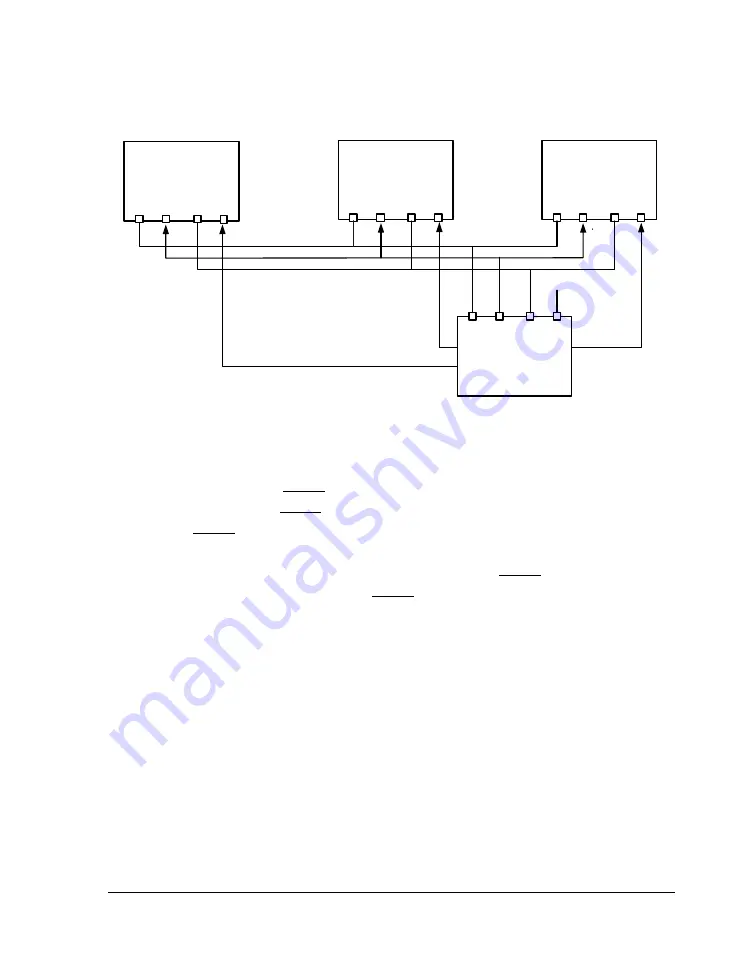

Figure 10-8. Single Master, Multiple Slave Configuration

MISO

SPICLK

MOSI

SPIDS

SLAVE DEVICE

MISO

SPICLK

MOSI

SPIDS

SLAVE DEVICE

MISO

SPICLK

MOSI

SPIDS

SLAVE DEVICE

MISO

SPICLK

MOSI

SPIDS

MASTER

DEVICE

FLAG

FLAG

FLAG

VDD

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...