ADSP-2126x SHARC Processor Hardware Reference

13-9

Precision Clock Generator

Pulse Width

Pulse width is the number of input clock periods for which the frame sync

output is

HIGH

. Pulse width should be less than the divisor of the frame

sync. The pulse width of frame sync A is specified in bits 15–0 of the

PCG_PW

register and the pulse width of frame sync B is specified in bits

31–16 of the

PCG_PW

register.

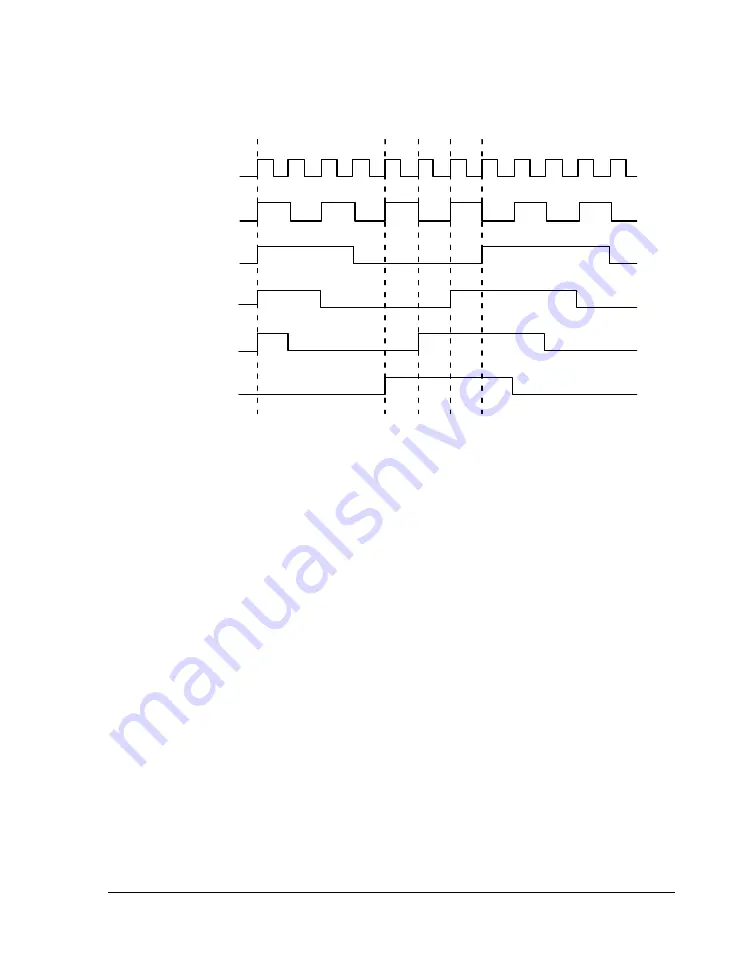

Figure 13-3. Adjusting Frame Sync Phase Shift

FRAME SY NC OUTPUT

(PHAS E SHIFT = DIVISOR -1)

CLOCK INPUT

(FOR BO TH CLO CK

AND FRAME SYNC)

ENABLE

FRAME SYNC OUTPUT

(PHASE SHIFT = 0)

FRAME SYNC OUTPUT

(PHASE SHIFT = 1)

CLO CK OUTPUT

FRAME SYNC OUTPUT

(PHASE SHIFT = 2)

OTHER VALUES:

CLOCK DIVIS OR = 2

FRAME SY NC DIVISOR = 8

P ULSE WIDTH = 4

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...