Boundary-Scan Architecture

B-4

ADSP-BF59x Blackfin Processor Hardware Reference

Note:

• The TAP controller enters the test-logic-reset state when

TMS

is

held high after five

TCK

cycles.

• The TAP controller enters the test-logic-reset state when

TRST

is

asynchronously asserted.

• An external system reset does not affect the state of the TAP con-

troller, nor does the state of the TAP controller affect an external

system reset.

Instruction Register

The instruction register is five bits wide and accommodates up to 32

boundary-scan instructions.

The instruction register holds both public and private instructions. The

JTAG standard requires some of the public instructions; other public

instructions are optional. Private instructions are reserved for the manu-

facturer’s use.

The binary decode column of

Table B-2

lists the decode for the public

instructions. The register column lists the serial scan paths.

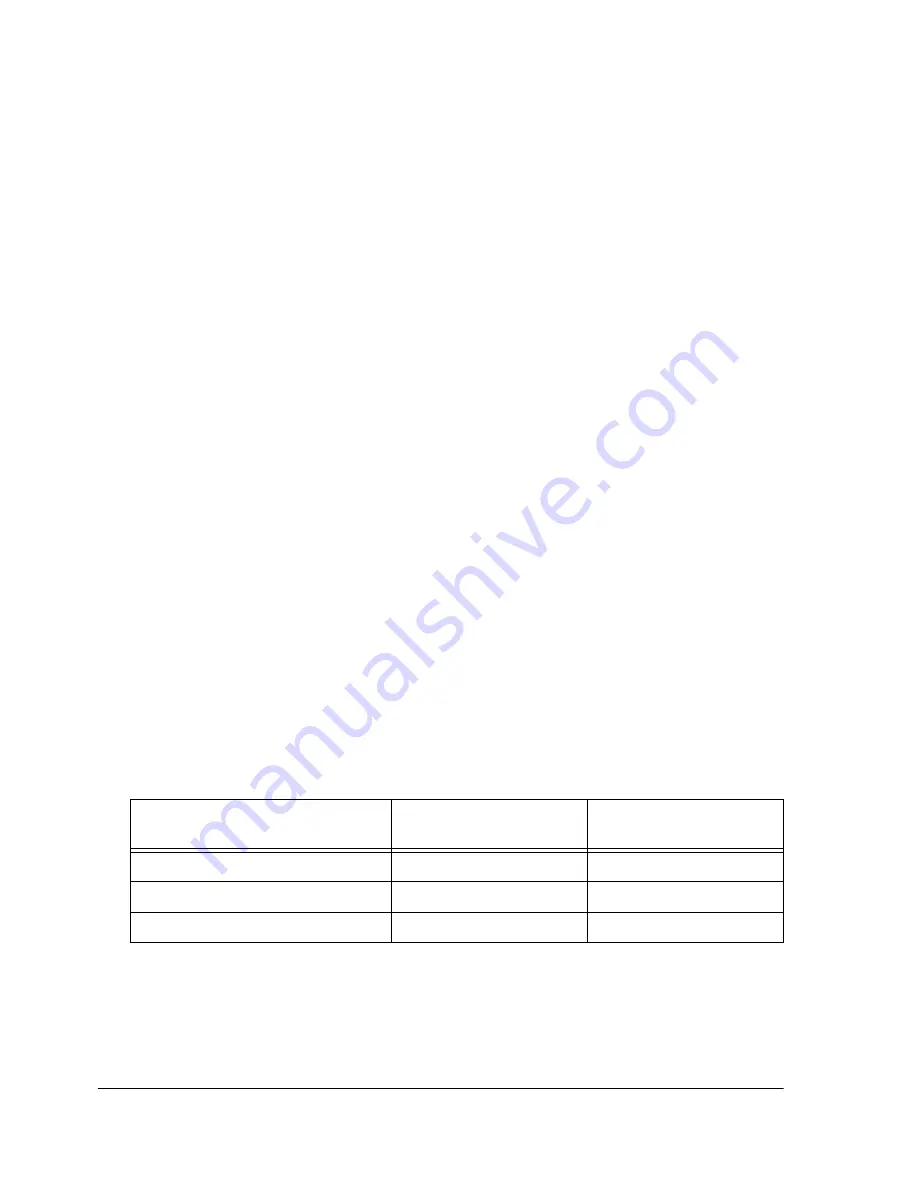

Table B-2. Decode for Public JTAG-Scan Instructions

Instruction Name

Binary Decode

01234

Register

EXTEST

00000

Boundary-Scan

SAMPLE/PRELOAD

10000

Boundary-Scan

BYPASS

11111

Bypass

Summary of Contents for ADSP-BF59x Blackfin

Page 64: ...Development Tools 1 22 ADSP BF59x Blackfin Processor Hardware Reference...

Page 74: ...Processor Specific MMRs 2 10 ADSP BF59x Blackfin Processor Hardware Reference...

Page 244: ...Programming Examples 6 40 ADSP BF59x Blackfin Processor Hardware Reference...

Page 700: ...Programming Examples 16 78 ADSP BF59x Blackfin Processor Hardware Reference...

Page 738: ...Boundary Scan Architecture B 8 ADSP BF59x Blackfin Processor Hardware Reference...