UG-1262

Rev. B | Page 38 of 312

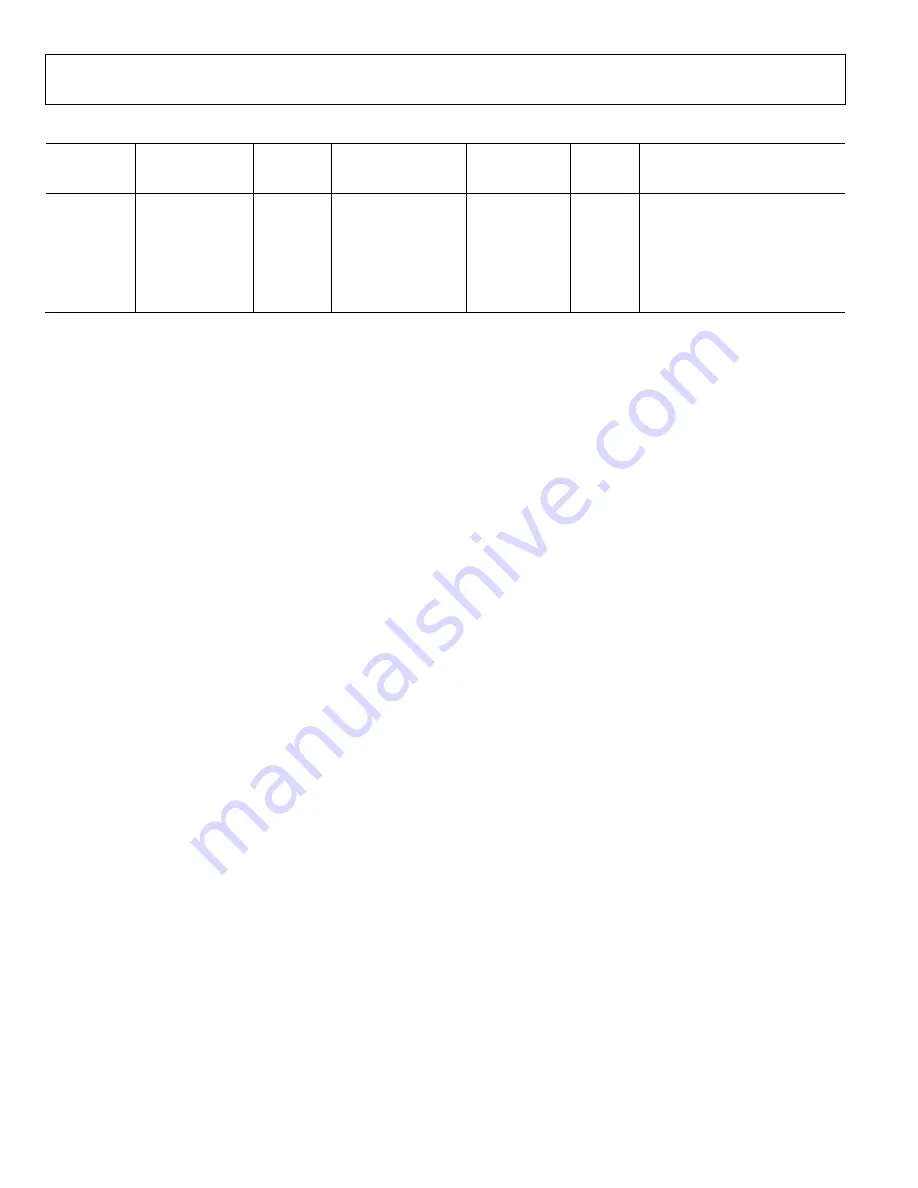

Table 33. Digital Die Reset Implications

Reset

Reset External

Pins to Default

State

Execute

Kernel

Reset All MMRs

Except RST_STAT

Register

Reset All

Peripherals

Valid

SRAM

RST_STAT Register After Reset

Event

Software Yes

1

Yes

Yes

Yes

Yes/No

2

RST_STAT, Bit 3 = 1

Watchdog Yes

Yes Yes

Yes

Yes/No

2

RSTSTA, Bit 2 = 1

External

Reset Pin

Yes Yes

Yes

Yes

Yes/No

2

RST_STAT, Bit 1 = 1

POR Yes

Yes

Yes

Yes

No

RST_STAT, Bit 0 = 1 and RST_STAT,

Bits[5:4] have information on the

cause of POR reset

1

The GPIOx pins return to their default state (same as a POR event).

2

Random access memory (RAM) is not valid in the case of a reset following a UART download.

Software Reset Command

The ARM Cortex-M3 supports a software reset command. Call the reset by using the following CMSIS library function:

NVIC_SystemReset(); // Call Software reset

This function involves a write the SYSRESETREQ bit in the Cortex AIRCR register. See the ARM Cortex-M3 user manual for details on

this register. When a software reset of the digital die is called, the chip is reset and all registers on both die return to their default states.