ADV7181B

Rev. B | Page 12 of 100

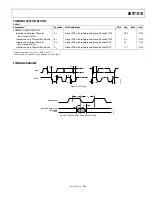

Table 7. Pin Function Descriptions

Pin No.

Mnemonic

Type

Description

3, 10, 24, 34, 57

DGND

G

Digital Ground.

32, 37, 43, 45

AGND

G

Analog Ground.

4, 11

DVDDIO

P

Digital I/O Supply Voltage (3.3 V).

23, 58

DVDD

P

Digital Core Supply Voltage (1.8 V).

40

AVDD

P

Analog Supply Voltage (3.3 V).

31

PVDD

P

PLL Supply Voltage (1.8 V).

35, 36, 46 to 49

AIN1 to AIN6

I

Analog Video Input Channels.

12, 13, 27, 28,

33, 50, 55, 56

NC

No Connect Pins.

5 to 8, 14 to 19,

25, 26, 59 to 62

P0 to P15

O

Video Pixel Output Port.

2

HS

O

Horizontal Synchronization Output Signal.

64

VS

O

Vertical Synchronization Output Signal.

63

FIELD

O

Field Synchronization Output Signal.

1

INTRQ

O

Interrupt Request Output. Interrupt occurs when certain signals are detected on the input

video. See the interrupt register map in Table 83.

53 SDA

I/O

I

2

C Port Serial Data Input/Output Pin.

54 SCLK

I

I

2

C Port Serial Clock Input. Maximum clock rate of 400 kHz.

52 ALSB

I

This pin selects the I

2

C address for the ADV7181B. ALSB set to a Logic 0 sets the address for a

write as 0x40; for ALSB set to a logic high, the address selected is 0x42.

51

RESET

I

System Reset Input, Active Low. A minimum low reset pulse width of 5 ms is required to reset

the ADV7181B circuitry.

20 LLC

O

This is a line-locked output clock for the pixel data output by the ADV7181B. Nominally 27 MHz,

but varies up or down according to video line length.

22 XTAL

I

This is the input pin for the 28.6363 MHz crystal, or can be overdriven by an external 3.3 V,

27 MHz clock oscillator source. In crystal mode, the crystal must be a fundamental crystal.

21 XTAL1

O

This pin should be connected to the 28.6363 MHz crystal or left as a no connect if an external

3.3 V, 27 MHz clock oscillator source is used to clock the ADV7181B. In crystal mode, the crystal

must be a fundamental crystal.

29

PWRDN

I

A logic low on this pin places the ADV7181B in power-down mode. Refer to the I2C Register

Maps section for more options on power-down modes for the ADV7181B.

30 ELPF

I

The recommended external loop filter must be connected to this ELPF pin, as shown in

Figure 45.

9 SFL

O

Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the

subcarrier frequency when this decoder is connected to any Analog Devices digital video

encoder.

41 REFOUT

O

Internal Voltage Reference Output. Refer to Figure 45 for a recommended capacitor network for

this pin.

42 CML

O

The CML pin is a common-mode level for the internal ADCs. Refer to Figure 45 for a

recommended capacitor network for this pin.

38, 39

CAPY1, CAPY2

I

ADC’s Capacitor Network. Refer to Figure 45 for a recommended capacitor network for this pin.

44

CAPC2

I

ADC’s Capacitor Network. Refer to Figure 45 for a recommended capacitor network for this pin.