ADV7181B

Rev. B | Page 14 of 100

Table 8. Manual Mux Settings for All ADCs (SETADC_sw_man_en = 1)

ADC0_sw[3:0]

ADC0 Connected to

ADC1_sw[3:0]

ADC1 Connected to

ADC2_sw[3:0]

ADC2 Connected to:

0000

No connection

0000

No connection

0000

No connection

0001 AIN2

0001 No

connection

0001 No

connection

0010

No connection

0010

No connection

0010

No connection

0011

No connection

0011

No connection

0011

No connection

0100

AIN4 0100

AIN4 0100

No

connection

0101

AIN6 0101

AIN6 0101

AIN6

0110

No connection

0110

No connection

0110

No connection

0111

No connection

0111

No connection

0111

No connection

1000

No connection

1000

No connection

1000

No connection

1001 AIN1

1001 No

connection

1001 No

connection

1010

No connection

1010

No connection

1010

No connection

1011

No connection

1011

No connection

1011

No connection

1100

AIN3 1100

AIN3 1100

No

connection

1101

AIN5 1101

AIN5 1101

AIN5

1110

No connection

1110

No connection

1110

No connection

1111

No connection

1111

No connection

1111

No connection

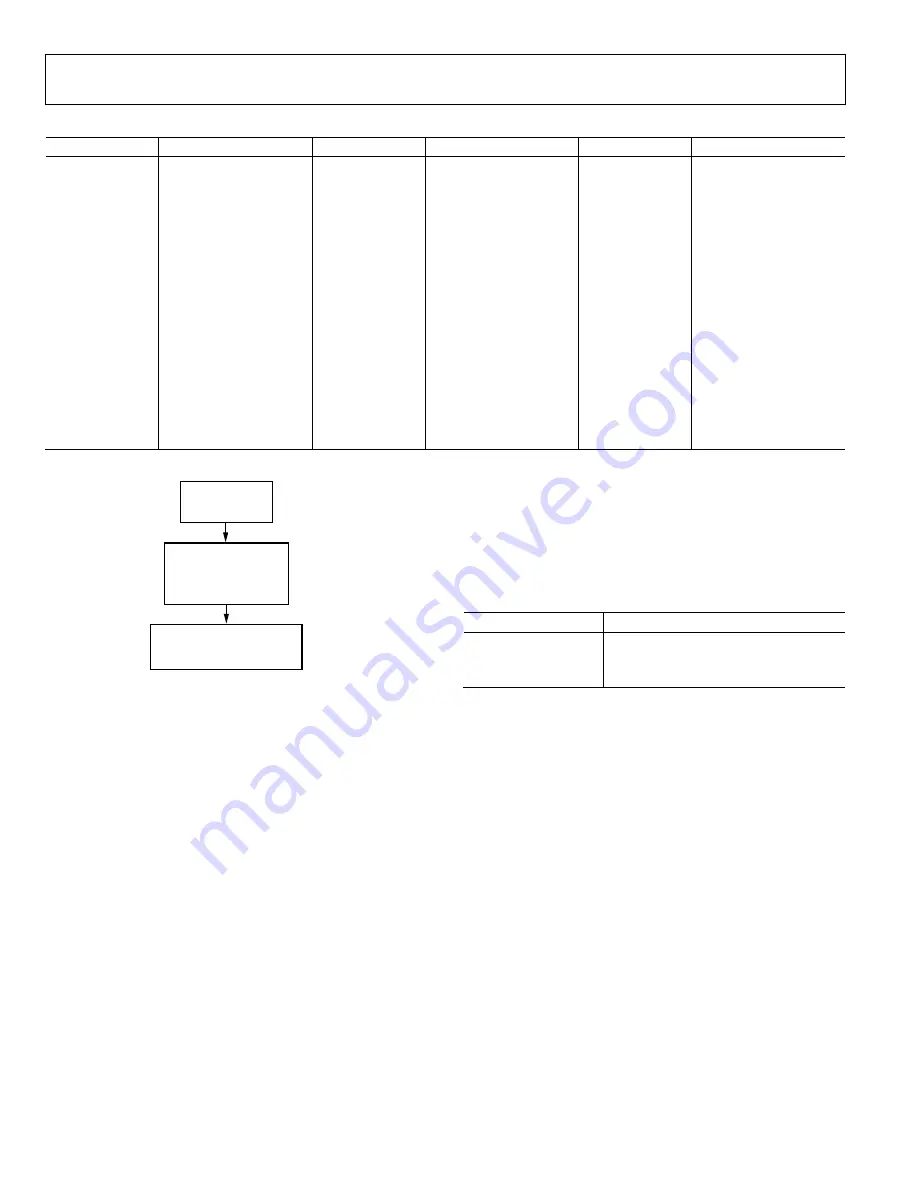

CONNECTING

ANALOG SIGNALS

TO ADV7181B

SET INSEL[3:0] TO

CONFIGURE ADV7181B TO

DECODE VIDEO FORMAT:

CVBS: 0000

YC: 0110

YPrPb: 1001

CONFIGURE ADC INPUTS USING

MUXING CONTROL BITS

(ADC_sw_man_en, ADC0_sw,

ADC1_sw, ADC2_sw)

04984-006

Figure 6. Input Muxing Overview

INSEL[3:0] Input Selection, Address 0x00[3:0]

The INSEL bits allow the user to select the input format. It

configures the standard definition processor core to process

CVBS (Comp), S-Video (Y/C), or Component (YPrPb) format.

Table 9. Standard Definition Processor Format Selection,

INSEL[3:0]

INSEL[3:0] Video

Format

0000 Composite

0110 Y/C

1001 YPrPb