ADV7181B

Rev. B | Page 44 of 100

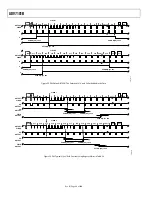

FIELD 1

OUTPUT

VIDEO

H

V

F

622

623

624

625

1

2

3

4

5

6

7

8

9

10

22

23

24

PVBEG[4:0] = 0x5

PVEND[4:0] = 0x4

PFTOG[4:0] = 0x3

FIELD 2

OUTPUT

VIDEO

H

V

F

PVBEG[4:0] = 0x5

PVEND[4:0] = 0x4

PFTOG[4:0] = 0x3

310

311

312

313

314

315

316

317

318

319

320

321

322

335

336

337

04984-025

Figure 25. PAL Default (BT.656). The Polarity of H, V, and F is Embedded in the Data

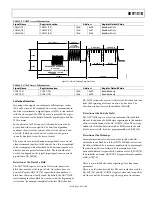

FIELD 1

622

623

624

625

1

2

3

4

5

6

7

8

9

10

11

23

24

310

311

312

313

314

315

316

317

318

319

320

321

322

323

336

337

PVBEG[4:0] = 0x1

PVEND[4:0] = 0x4

PFTOG[4:0] = 0x6

FIELD 2

OUTPUT

VIDEO

FIELD

OUTPUT

HS

OUTPUT

VS

OUTPUT

OUTPUT

VIDEO

FIELD

OUTPUT

HS

OUTPUT

VS

OUTPUT

PVBEG[4:0] = 0x1

PVEND[4:0] = 0x4

PFTOG[4:0] = 0x6

04984-026

Figure 26. PAL Typical Vsync/Field Positions Using Register Writes in Table 56