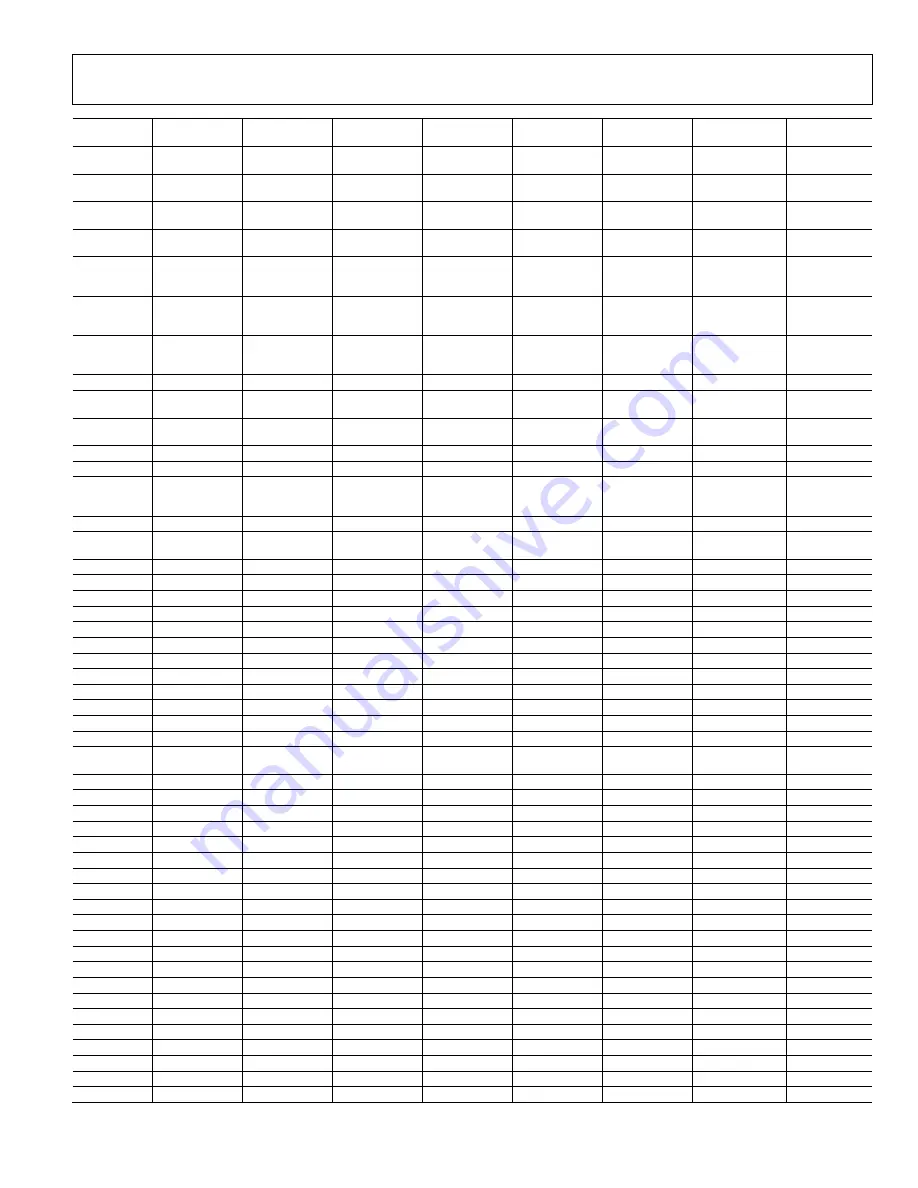

ADV7181B

Rev. B | Page 65 of 100

Register

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Luma Gain

Control 2

LMG.7 LMG.6 LMG.5 LMG.4 LMG.3 LMG.2 LMG.1 LMG.0

Vsync Field

Control 1

NEWAVMODE

HVSTIM

Vsync Field

Control 2

VSBHO

VSBHE

Vsync Field

Control 3

VSEHO

VSEHE

Hsync

Position

Control 1

HSB.10

HSB.9 HSB.8

HSE.10

HSE.9 HSE.8

Hsync

Position

Control 2

HSB.7 HSB.6 HSB.5 HSB.4 HSB.3 HSB.2 HSB.1 HSB.0

Hsync

Position

Control 3

HSE.7 HSE.6 HSE.5 HSE.4 HSE.3 HSE.2 HSE.1 HSE.0

Polarity

PHS

PVS

PF

PCLK

NTSC Comb

Control

CTAPSN.1

CTAPSN.0

CCMN.2 CCMN.1 CCMN.0 YCMN.2 YCMN.1 YCMN.0

PAL Comb

Control

CTAPSP.1

CTAPSP.0

CCMP.2 CCMP.1 CCMP.0 YCMP.2 YCMP.1 YCMP.0

ADC

Control

PWRDN_AD

C_0

PWRDN_AD

C_1

PWRDN_ADC_2

Reserved

Manual

Window

Control

CKILLTHR.2 CKILLTHR.1 CKILLTHR.0

Reserved

Resample

Control

SFL_INV

Reserved

Gemstar

Ctrl

1

GDECEL.15 GDECEL.14 GDECEL.13 GDECEL.12 GDECEL.11 GDECEL.10 GDECEL.9 GDECEL.8

Gemstar

Ctrl

2

GDECEL.7 GDECEL.6 GDECEL.5 GDECEL.4 GDECEL.3 GDECEL.2 GDECEL.1 GDECEL.0

Gemstar Ctrl 3

GDECOL.15

GDECOL.14

GDECOL.13

GDECOL.12 GDECOL.11 GDECOL.10 GDECOL.9 GDECOL.8

Gemstar

Ctrl

4

GDECOL.7 GDECOL.6 GDECOL.5 GDECOL.4 GDECOL.3 GDECOL.2 GDECOL.1 GDECOL.0

Gemstar

Ctrl

5

GDECAD

CTI DNR Ctrl 1

DNR_EN

CTI_AB.1 CTI_AB.0 CTI_AB_EN

CTI_EN

CTI DNR Ctrl 2

CTI_C_TH.7

CTI_C_TH.6

CTI_C_TH.5

CTI_C_TH.4 CTI_C_TH.3 CTI_C_TH.2 CTI_C_TH.1 CTI_C_TH.0

Reserved

CTI DNR Ctrl 4

DNR_TH.7

DNR_TH.6

DNR_TH.5

DNR_TH.4 DNR_TH.3 DNR_TH.2 DNR_TH.1 DNR_TH.0

Lock

Count

FSCLE SRLS COL.2 COL.1 COL.0 CIL.2 CIL.1 CIL.0

Reserved

Free Run Line

Length 1

LLC_PAD_SEL.2

LLC_PAD_SEL.1 LLC_PAD_SEL.0

Reserved

VBI

Info

CGMSD

EDTVD

CCAPD

WSSD

WSS

1

WSS1.7 WSS1.6 WSS1.5 WSS1.4 WSS1.3 WSS1.2 WSS1.1 WSS1.0

WSS

2

WSS2.7 WSS2.6 WSS2.5 WSS2.4 WSS2.3 WSS2.2 WSS2.1 WSS2.0

EDTV

1

EDTV1.7 EDTV1.6 EDTV1.5 EDTV1.4 EDTV1.3 EDTV1.2 EDTV1.1 EDTV1.0

EDTV

2

EDTV2.7 EDTV2.6 EDTV2.5 EDTV2.4 EDTV2.3 EDTV2.2 EDTV2.1 EDTV2.0

EDTV

3

EDTV3.7 EDTV3.6 EDTV3.5 EDTV3.4 EDTV3.3 EDTV3.2 EDTV3.1 EDTV3.0

CGMS

1

CGMS1.7 CGMS1.6 CGMS1.5 CGMS1.4 CGMS1.3 CGMS1.2 CGMS1.1 CGMS1.0

CGMS

2

CGMS2.7 CGMS2.6 CGMS2.5 CGMS2.4 CGMS2.3 CGMS2.2 CGMS2.1 CGMS2.0

CGMS

3

CGMS3.7 CGMS3.6 CGMS3.5 CGMS3.4 CGMS3.3 CGMS3.2 CGMS3.1 CGMS3.0

CCAP

1

CCAP1.7 CCAP1.6 CCAP1.5 CCAP1.4 CCAP1.3 CCAP1.2 CCAP1.1 CCAP1.0

CCAP 2

CCAP2.7

CCAP2.6

CCAP2.5

CCAP2.4

CCAP2.3

CCAP2.2

CCAP2.1

CCAP2.0

Letterbox 1

LB_LCT.7

LB_LCT.6

LB_LCT.5

LB_LCT.4

LB_LCT.3

LB_LCT.2

LB_LCT.1

LB_LCT.0

Letterbox 2

LB_LCM.7

LB_LCM.6

LB_LCM.5

LB_LCM.4

LB_LCM.3

LB_LCM.2

LB_LCM.1

LB_LCM.0

Letterbox 3

LB_LCB.7

LB_LCB.6

LB_LCB.5

LB_LCB.4

LB_LCB.3

LB_LCB.2

LB_LCB.1

LB_LCB.0

Reserved

CRC

Enable

CRC_ENABLE

Reserved

ADC

Switch

1

ADC1_SW.3 ADC1_SW.2 ADC1_SW.1 ADC1_SW.0 ADC0_SW.3 ADC0_SW.2 ADC0_SW.1 ADC0_SW.0

ADC

Switch

2

ADC_SW_M

AN

ADC2_SW.3

ADC2_SW.2

ADC2_SW.1

ADC2_SW.0

Reserved