ADV7181B

Rev. B | Page 8 of 100

TIMING SPECIFICATIONS

Guaranteed by characterization. A

VDD

= 3.15 V to 3.45 V, D

VDD

= 1.65 V to 2.0 V, D

VDDIO

= 3.0 V to 3.6 V, P

VDD

= 1.65 V to 2.0 V;

operating temperature range, unless otherwise noted.

Table 3.

Parameter

1, 2

Symbol

Test

Conditions

Min

Typ

Max

Unit

SYSTEM CLOCK AND CRYSTAL

Nominal Frequency

27.00

MHz

Frequency Stability

±50

ppm

I

2

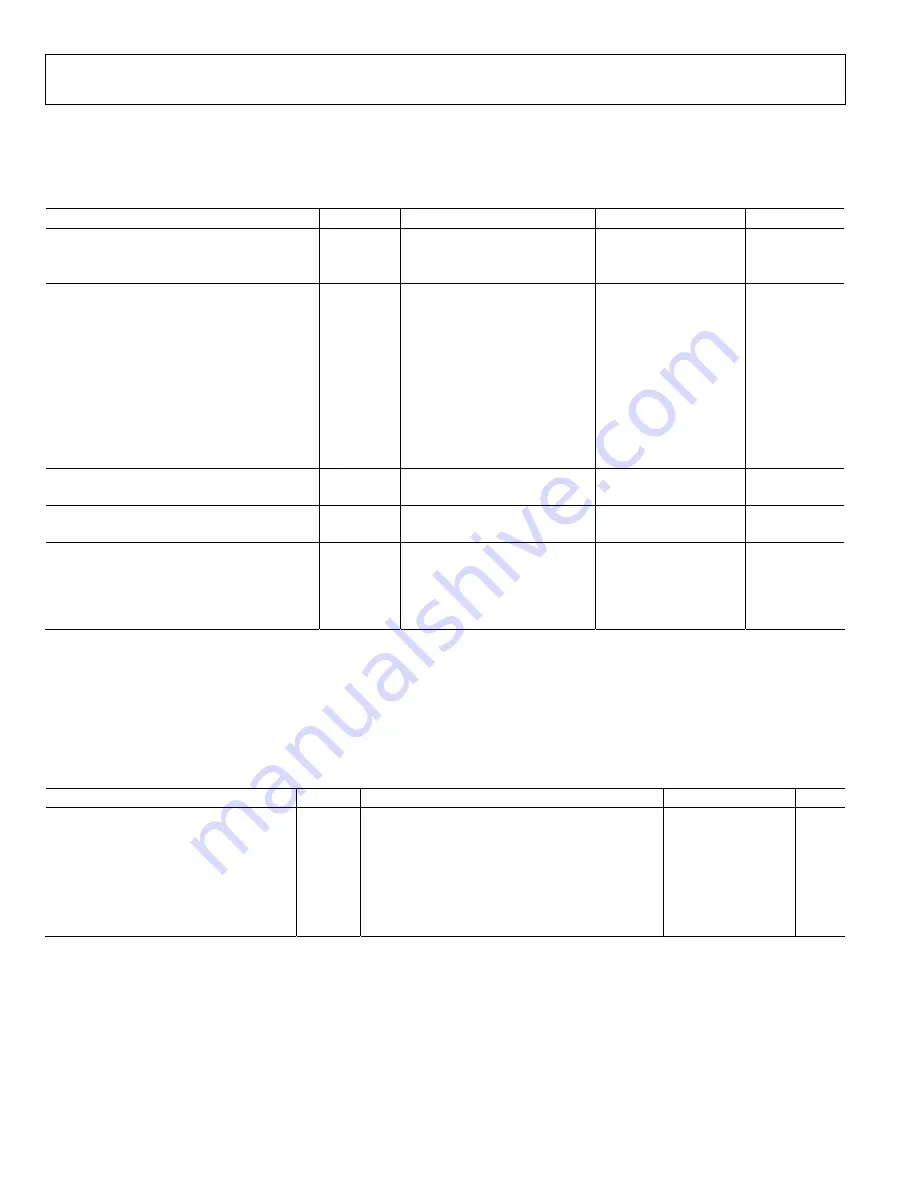

C PORT

SCLK Frequency

400

kHz

SCLK Min Pulse Width High

t

1

0.6

μs

SCLK Min Pulse Width Low

t

2

1.3

μs

Hold Time (Start Condition)

t

3

0.6

μs

Setup Time (Start Condition)

t

4

0.6

μs

SDA Setup Time

t

5

100

ns

SCLK and SDA Rise Time

t

6

300

ns

SCLK and SDA Fall Time

t

7

300

ns

Setup Time for Stop Condition

t

8

0.6

μs

RESET FEATURE

Reset Pulse Width

5

ms

CLOCK OUTPUTS

LLC1 Mark Space Ratio

t

9

:t

10

45:55

55:45

% duty cycle

DATA AND CONTROL OUTPUTS

Data Output Transitional Time

t

11

Negative clock edge to start of

valid data (t

ACCESS

= t

10

– t

11

)

3.4

ns

Data Output Transitional Time

t

12

End of valid data to negative

clock edge (t

HOLD

= t

9

+ t

12

)

2.4

ns

1

Temperature range: T

MIN

to T

MAX

, –40°C to +85°C.

2

The min/max specifications are guaranteed over this range.

ANALOG SPECIFICATIONS

Guaranteed by characterization. A

VDD

= 3.15 V to 3.45 V, D

VDD

= 1.65 V to 2.0 V, D

VDDIO

= 3.0 V to 3.6 V, P

VDD

= 1.65 V to 2.0 V;

operating temperature range, unless otherwise noted. Recommended analog input video signal range: 0.5 V to 1.6 V, typically 1 V p-p.

Table 4.

Parameter

1, 2

Symbol

Test

Conditions

Min

Typ

Max

Unit

CLAMP CIRCUITRY

External Clamp Capacitor

0.1

μF

Input Impedance

Clamps switched off

10

MΩ

Large Clamp Source Current

0.75

mA

Large Clamp Sink Current

0.75

mA

Fine Clamp Source Current

60

μA

Fine Clamp Sink Current

60

μA

1

Temperature range: T

MIN

to T

MAX

, –40°C to +85°C

2

The min/max specifications are guaranteed over this range.