ADV7181B

Rev. B | Page 85 of 100

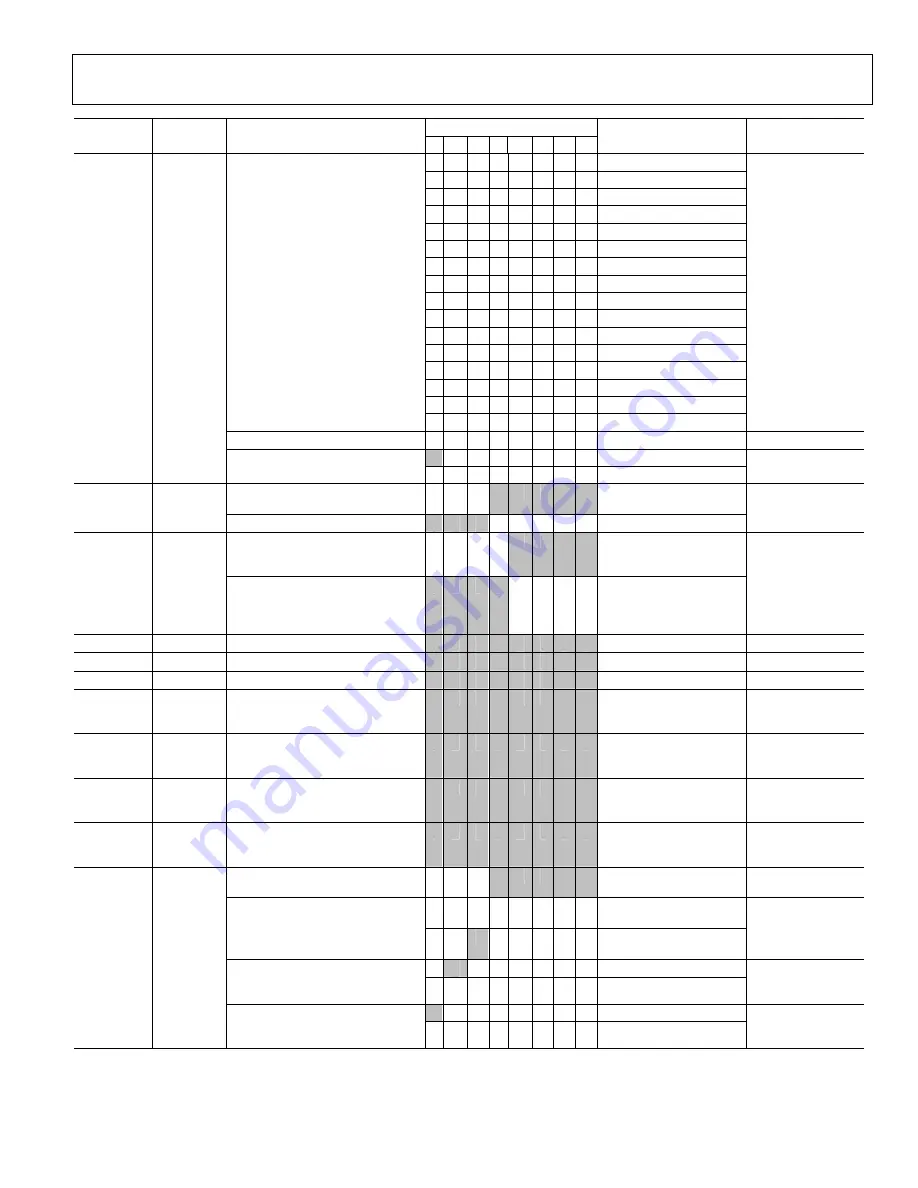

Bits

Subaddress

Register

Bit Description

7

6 5

4

3 2

1

0 Comments Notes

0 0 0 0 No

connection

0 0 0 1 No

connection

0 0 1 0 No

connection

0 0 1 1 No

connection

0 1 0 0 No

connection

0 1 0 1 AIN6

0 1 1 0 No

connection

0 1 1 1 No

connection

1 0 0 0 No

connection

1 0 0 1 No

connection

1 0 1 0 No

connection

1 0 1 1 No

connection

1 1 0 0 No

connection

1 1 0 1 AIN5

1 1 1 0 No

connection

ADC2_SW[3:0]. Manual muxing

control for ADC2.

1 1 1 1 No

connection

SETADC_sw_

man_en = 1.

Reserved.

x

x

x

0

Disable

0xC4 ADC

SWITCH 2

ADC_SW_MAN_EN. Enable manual

setting of the input signal muxing.

1

Enable

LB_TH[4:0]. Sets the threshold value

that determines if a line is black.

0

1

1

0

0

Default threshold for the

detection of black lines

0xDC Letterbox

Control 1

Reserved.

1

0

1

Set as default

LB_EL[3:0]. Programs the end line of

the activity window for LB detection

(end of field).

1

1

0

0

LB detection ends with

the last line of active video

on a field.;1100b: 262/525

0xDD Letterbox

Control 2

LB_SL[3:0]. Program the start line of

the activity window for LB detection

(start of field).

0

1

0

0

Letterbox

detection

aligned with the start of

active video; 0100b:

23/286 NTSC

0xDE

Reserved.

0

0

0

0

0

0

0

0

0xDF

Reserved.

0

0

0

0

0

0

0

0

0xE0

Reserved.

0

0

0

1

0

1

0

0

0xE1 SD

Offset

Cb

SD_OFF_CB[7:0]. Adjusts the hue by

selecting the offset for the Cb

channel.

1

0

0

0

0

0

0

0

0xE2

SD Offset

Cr

SD_OFF_CR[7:0]. Adjusts the hue by

selecting the offset for the Cr

channel.

1

0

0

0

0

0

0

0

0xE3 SD

Saturation

Cb

SD_SAT_CB[7:0]. Adjusts the

saturation of the picture by

affecting gain on the Cb channel.

1

0

0

0

0

0

0

0

Chroma gain = 0 dB

0xE4 SD

Saturation

Cr

SD_SAT_CR[7:0]. Adjusts the

saturation of the picture by

affecting gain on the Cr channel.

1

0

0

0

0

0

0

0

Chroma gain = 0 dB

NVBEG[4:0]. How many lines after

l

COUNT

rollover to set V high.

0

0

1

0

1

NTSC default (BT.656)

0

Set to low when manual

programming

NVBEGSIGN.

1

Not suitable for user

programming

0 No

delay

NVBEGDELE. Delay V bit going high

by one line relative to NVBEG (even

field).

1

Additional delay by 1 line

0

No

delay

0xE5

NTSC V Bit

Begin

NVBEGDELO. Delay V bit going high

by one line relative to NVBEG (odd

field).

1

Additional delay by 1 line