ADV7181B

Rev. B | Page 87 of 100

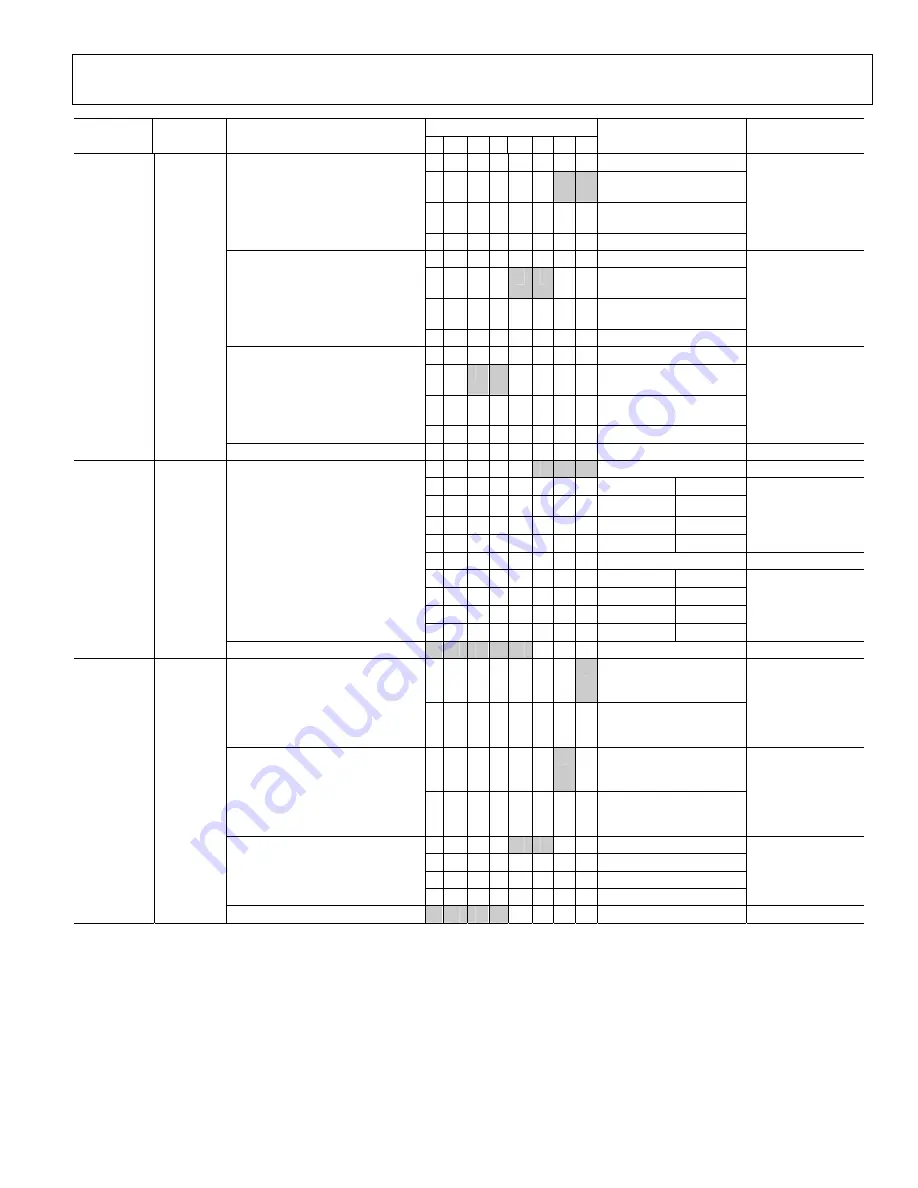

Bits

Subaddress

Register

Bit Description

7

6 5

4

3 2

1

0 Comments Notes

0

0

Low drive strength (1x)

0

1 Medium-low

drive

strength (2x)

1 0 Medium-high

drive

strength (3x)

DR_STR_S[1:0]. Select the drive

strength for the Sync output signals.

1

1

High drive strength (4x)

0

0

Low drive strength (1x)

0

1 Medium-low

drive

strength (2x)

1 0 Medium-high

drive

strength (3x)

DR_STR_C[1:0]. Select the drive

strength for the Clock output signal.

1

1

High drive strength (4x)

0

0

Low drive strength (1x)

0

1

Medium-low

drive

strength (2x)

1 0

Medium-high

drive

strength (3x)

DR_STR[1:0]. Select the drive

strength for the data output signals.

Can be increased or decreased for

EMC or crosstalk reasons.

1

1

High drive strength (4x)

0xF4 Drive

Strength

Reserved. x

x

No

delay

0

0

0

Bypass mode

0 dB.

2 MHz

5 MHz

0 0 1

−

3 dB

−

2 dB

0 1 0

−

6 dB

+3.5 dB

0 1 1

−

10 dB

+5 dB

NTSC filters.

1 0 0 Reserved

3 MHz

6 MHz

1 0 1

−

2 dB

+2 dB

1 1 0

−

5 dB

+3 dB

IFFILTSEL[2:0]. IF filter selection for

Pal and NTSC.

1 1 1

−

7 dB

+5 dB

PAL filters.

0xF8 IF

Comp

Control

Reserved.

0

0

0

0

0

0 Limit

maximum

Vsync

frequency to 66.25 Hz

(475 lines/frame)

EXTEND_VS_MAX_FREQ.

1 Limit

maximum

Vsync

frequency to 70.09 Hz

(449 lines/frame)

0

Limit minimum Vsync

frequency to 42.75 Hz

(731 lines/frame)

EXTEND_VS_MIN_FREQ.

1

Limit minimum Vsync

frequency to 39.51 Hz

(791 lines/frame)

0

0

Auto coast mode

0

1

50 Hz coast mode

1

0

60 Hz coast mode

VS_COAST_MODE[1:0].

1 1 Reserved

This value sets up

the output coast

frequency.

0xF9 VS

Mode

Control

Reserved.

0

0

0

0