ADV7181B

Rev. B | Page 16 of 100

GLOBAL PIN CONTROL

Three-State Output Drivers

TOD, Address 0x03[6]

This bit allows the user to three-state the output drivers of the

ADV7181B.

Upon setting the TOD bit, the P15 to P0, HS, VS, FIELD, and

SFL pins are three-stated.

The timing pins (HS/VS/FIELD) can be forced active via the

TIM_OE bit. For more information on three-state control, refer

to the Three-State LLC Driver and the Timing Signals Output

Enable sections.

Individual drive strength controls are provided via the

DR_STR_XX bits.

When TOD is 0 (default), the output drivers are enabled.

When TOD is 1, the output drivers are three-stated.

Three-State LLC Driver

TRI_LLC, Address 0x1D[7]

This bit allows the output drivers for the LLC pin of the

ADV7181B to be three-stated. For more information on three-

state control, see the Three-State Output Drivers and the

Timing Signals Output Enable sections.

Individual drive strength controls are provided via the

DR_STR_XX bits.

When TRI_LLC is 0 (default), the LLC pin drivers work

according to the DR_STR_C[1:0] setting (pin enabled).

When TRI_LLC is 1, the LLC pin drivers are three-stated.

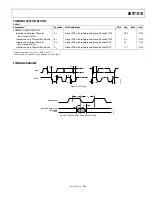

Timing Signals Output Enable

TIM_OE, Address 0x04[3]

The TIM_OE bit should be regarded as an addition to the TOD

bit. Setting it high forces the output drivers for HS, VS, and

FIELD into the active (driving) state even if the TOD bit is set.

If set to low, the HS, VS, and FIELD pins are three-state

dependent on the TOD bit. This functionality is useful if the

decoder is to be used as a timing generator only. This may be

the case if only the timing signals are to be extracted from an

incoming signal, or if the part is in free-run mode where a

separate chip can output, for instance, a company logo.

For more information on three-state control, see the Three-

State Output Drivers and the Three-State LLC Driver sections.

Individual drive strength controls are provided via the

DR_STR_XX bits.

When TIM_OE is 0 (default), HS, VS, and FIELD are three-

stated according to the TOD bit.

When TIM_OE is 1, HS, VS, and FIELD are forced active all the

time.

Drive Strength Selection (Data)

DR_STR[1:0] Address 0xF4[5:4]

For EMC and crosstalk reasons, it can be desirable to strengthen

or weaken the drive strength of the output drivers. The

DR_STR[1:0] bits affect the P[15:0] output drivers.

For more information on three-state control, refer to the Drive

Strength Selection (Clock) and the Drive Strength Selection

(Sync) sections.

Table 10. DR_STR Function

DR_STR[1:0] Description

00

Low drive strength (1×)

01 (default)

Medium low drive strength (2×)

10

Medium high drive strength (3×)

11

High drive strength (4×)

Drive Strength Selection (Clock)

DR_STR_C[1:0] Address 0xF4[3:2]

The DR_STR_C[1:0] bits can be used to select the strength of

the clock signal output driver (LLC pin). For more information,

refer to the Drive Strength Selection (Sync) and the Drive

Strength Selection (Data) sections.

Table 11. DR_STR_C Function

DR_STR[1:0] Description

00

Low drive strength (1×)

01 (default)

Medium low drive strength (2×)

10

Medium high drive strength (3×)

11

High drive strength (4×)

Drive Strength Selection (Sync)

DR_STR_S[1:0] Address 0xF4[1:0]

The DR_STR_S[1:0] bits allow the user to select the strength of

the synchronization signals with which HS, VS, and F are driven.

For more information, refer to the Drive Strength Selection

(Data) section.

Table 12. DR_STR_S Function

DR_STR[1:0] Description

00

Low drive strength (1×)

01 (default)

Medium low drive strength (2×).

10

Medium high drive strength (3×)

11

High drive strength (4×)