ADV7181B

Rev. B | Page 58 of 100

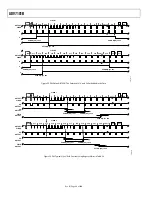

INTRQ_OP_SEL[1:0], Interrupt Duration Select

Address 0x40 (Interrupt Space)[1:0]

Table 76. INTRQ_OP_SEL

INTRQ_OP_SEL[1:0] Description

00

Open drain (default)

01

Drive low when active

10

Drive high when active

11 Reserved

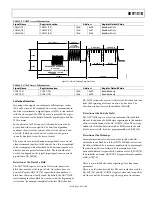

Multiple Interrupt Events

If Interrupt Event 1 occurs and then Interrupt Event 2 occurs

before the system controller has cleared or masked Interrupt

Event 1, the ADV7181B does not generate a second interrupt

signal. The system controller should check all unmasked

interrupt status bits since more than one can be active.

Macrovision Interrupt Selection Bits

The user can select between pseudo sync pulse and color stripe

detection as follows:

MV_INTRQ_SEL[1:0], Macrovision Interrupt Selection

Bits, Address 0x40 (Interrupt Space)[5:4]

Table 77. MV_INTRQ_SEL

MV_INTRQ_SEL[1:0] Description

00 Reserved

01

Pseudo sync only (default)

10 Color

stripe

only

11

Either pseudo sync or color stripe

Additional information relating to the interrupt system is

detailed in Table 83.