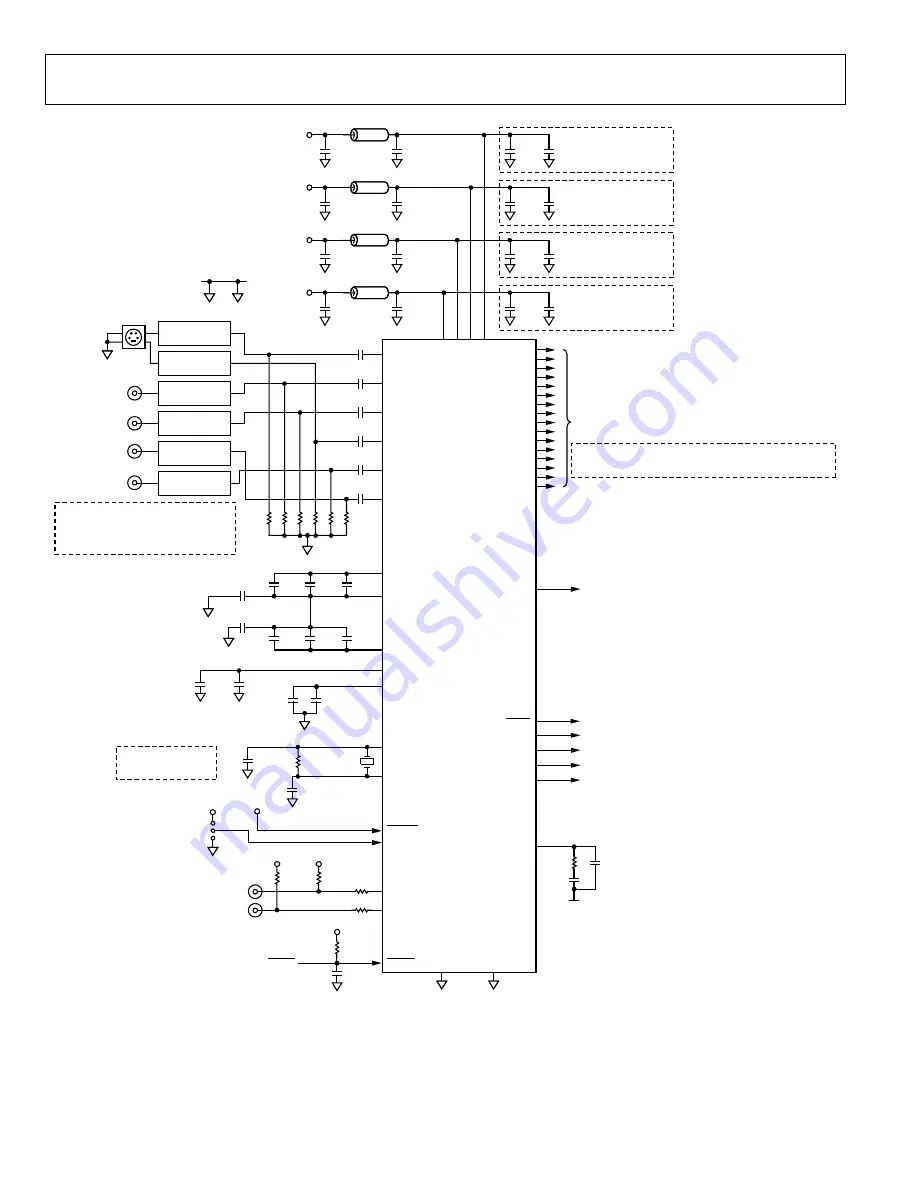

ADV7181B

Rev. B | Page 98 of 100

2k

Ω

2k

Ω

AGND

DGND

AGND

DGND

0.1

μ

F

DGND

0.01

μ

F

DGND

33

μ

F

DGND

10

μ

F

DGND

FERRITE BEAD

DVDDIO

(3.3V)

POWER SUPPLY

DECOUPLING FOR

EACH POWER PIN

0.1

μ

F

AGND

0.01

μ

F

AGND

33

μ

F

AGND

10

μ

F

AGND

FERRITE BEAD

PVDD

(1.8V)

POWER SUPPLY

DECOUPLING FOR

EACH POWER PIN

0.1

μ

F

AGND

0.01

μ

F

AGND

33

μ

F

AGND

10

μ

F

AGND

FERRITE BEAD

AVDD

(3.3V)

POWER SUPPLY

DECOUPLING FOR

EACH POWER PIN

0.1

μ

F

DGND

0.01

μ

F

DGND

33

μ

F

DGND

10

μ

F

DGND

FERRITE BEAD

DVDD

(1.8V)

POWER SUPPLY

DECOUPLING FOR

EACH POWER PIN

AGND DGND

DVDD

AVDD

PVDD

DVDDIO

AIN2

100nF

AIN1

100nF

AIN3

100nF

AIN4

100nF

AIN5

100nF

AIN6

100nF

AGND

75

Ω

75

Ω

75

Ω

75

Ω

75

Ω

75

Ω

+

CAPY1

CAPY2

AGND

0.1

μ

F

10

μ

F

0.1

μ

F

+

CAPC2

CML

AGND

0.1

μ

F

0.1nF

0.1nF

10

μ

F

0.1

μ

F

LLC

27MHz OUTPUT CLOCK

SFL

SFL O/P

HS

HS O/P

VS

VS O/P

FIELD

FIELD O/P

ELPF

1.69k

Ω

10nF

82nF

PVDD

DGND

DVDDIO

100nF

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

MULTI-FORMAT

PIXEL PORT

+

10

μ

F

0.1

μ

F

REFOUT

AGND

0.1

μ

F

10

μ

F

+

XTAL

47pF

DGND

XTAL1

ALSB

47pF

DGND

28.63636MHz

ADV7181B

DVDDIO

DVDDIO

SELECT I

2

C

ADDRESS

DVSS

PWRDN

MPU INTERFACE

CONTROL LINES

SCLK

SDA

33

Ω

33

Ω

DVDDIO

DVDDIO

4.7k

Ω

RESET

RESET

INTERRUPT O/P

INTRQ

ITU-R

8-BIT

P8

P15–

27MHz

@

DATA

PIXEL

BT.656

13.5MHz

@

DATA

PIXEL

BT.656

ITU-R

16-BIT

Cr

AND

Cb

P0

–

P7

13.5MHz

@

DATA

PIXEL

BT.656

ITU-R

16-BIT

Y2

AND

Y1

P8

–

P15

AIN3

S-VIDEO

Y

Pr

Pb

CBVS

ANTI-ALIAS

FILTER CIRCUIT

ANTI-ALIAS

FILTER CIRCUIT

ANTI-ALIAS

FILTER CIRCUIT

ANTI-ALIAS

FILTER CIRCUIT

ANTI-ALIAS

FILTER CIRCUIT

ANTI-ALIAS

FILTER CIRCUIT

RECOMMENDED ANTI-ALIAS FILTER

CIRCUIT IS SHOWN IN FIGURE 44 ON THE

PREVIOUS PAGE. THIS CIRCUIT INCLUDES

A 75

Ω

TERMINATION RESISTOR, INPUT

BUFFER AND ANTI-ALIASING FILTER.

CAPACITOR VALUES

ARE DEPENDENT

ON XTAL ATTRIBUTES.

04984-044

1M

Ω

Figure 45. Typical Connection Diagram