ADV8003 Hardware Manual

Rev. B, August 2013

183

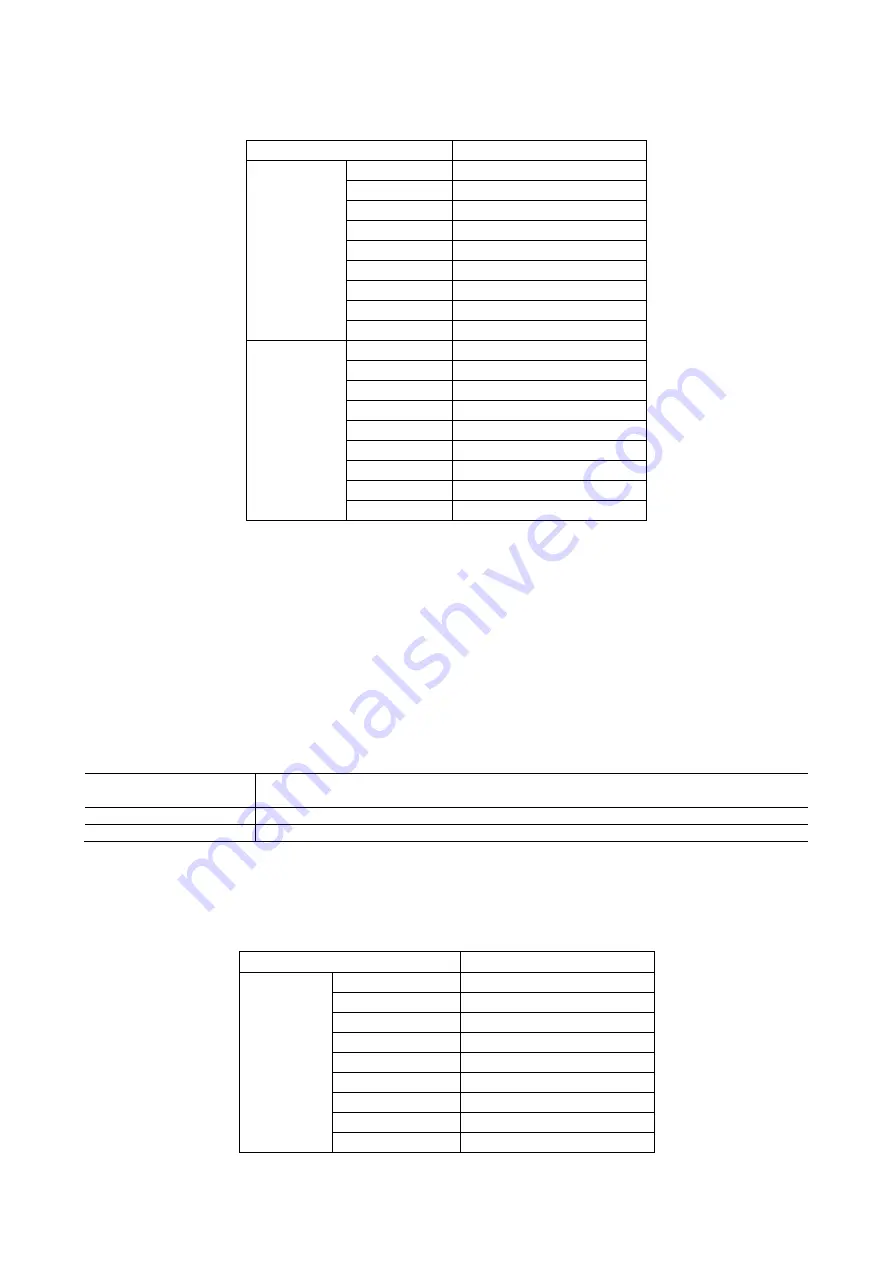

Video Timing

VID

1920x1080p24

32

1920x1080p25

33

1920x1080p30

34

720p100

41

576p100

42 or 43

720p120

47

480p120

48 or 49

576p200

52 or 53

480p240

56 or 57

VESA timing

VGA

200

SVGA

201

XGA

202

WXGA

203

SXGA

204

WXGA-2

205

UXGA

206

WXGA-3

207

WUXGA

208

Note

: The SVSP does not support the following formats:

•

1280x720p @ 23.97/24 Hz (CEA VIC 60)

•

1280x720p @ 25 Hz (CEA VIC 61)

•

1280x720p @ 29.97/30 Hz (CEA VIC 62)

svsp_autocfg_output_vid[7:0]

, Secondary VSP Map,

Address 0xE661[7:0]

This register is used to set the output timing VIC. If this register is 0, SVSP will use values in registers of svsp_dp_decount,

svsp_dp_hfrontporch, svsp_dp_hsynctime, svsp_dp_hbackporch, svsp_dp_activeline, svsp_dp_vfrontporch, svsp_dp_vsynctime,

svsp_dp_vbackporch, svsp_dp_hpolarity, svsp_dp_vpolarity and svsp_vout_fr to set output video.

Function

svsp_autocfg_output_v

id[7:0]

Description

0x00

Custom output video

0xXX

Output timing VIC

lists all the supported video timings and their VID. The 59.94/23.97 Hz timings have the same VID as the corresponding 60/24

Hz timing in the table.

Table 32: SVSP Supported Output Video Timing and VID

Video Timing

VID

CEA

640x480p60

1

720x480p60

2 or 3 or 14 or 15 or 35 or 36

720(1440)x240p60

8 or 9

720(2880)x240p60

12 or 13

1280x720p60

4

1920x1080i60

5

720x480i60

6 or 7 or 10 or 11

1920x1080p

16

720x576p50

17 or 18 or 29 or 30 or 37 or 38

Summary of Contents for ADV8003

Page 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Page 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Page 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Page 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Page 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Page 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Page 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Page 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Page 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Page 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Page 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Page 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Page 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Page 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Page 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Page 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Page 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Page 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Page 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Page 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Page 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Page 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Page 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Page 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Page 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Page 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Page 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Page 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Page 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Page 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Page 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Page 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Page 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Page 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Page 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...