ADV8003 Hardware Manual

Rev. B, August 2013

271

Function

spdif_sf[3:0]

Description

0000

44.1kHz

0001

NA

0010

48 kHz

0011

32kHz

0100

NA

0101

NA

0110

NA

0111

NA

1000

88.2kHz

1001

NA

1010

96kHz

1011

NA

1100

176.4kHz

1101

NA

1110

192kHz

1111

NA

6.11.2.3.

DSD Audio

The ADV8003 uses 1-bit Audio Sample packets to transmit DSD audio data across the HDMI link to the downstream sink. The ADV8003

supports up to six channels of DSD data which can be input onto six data lines clocked by the signal input to DSD_CLK.

The ADV8003 can be configured to receive a DSD stream by setting

to 0b010. The mode of the DSD stream input to

the ADV8003 can be set via the

field. The audio sampling frequency must be set via the

DSD clock input to SCLK has a frequency that is 64 times the audio sampling frequency programmed in the

field.

Refer to

for additional details on the DSD modes supported by the ADV8003.

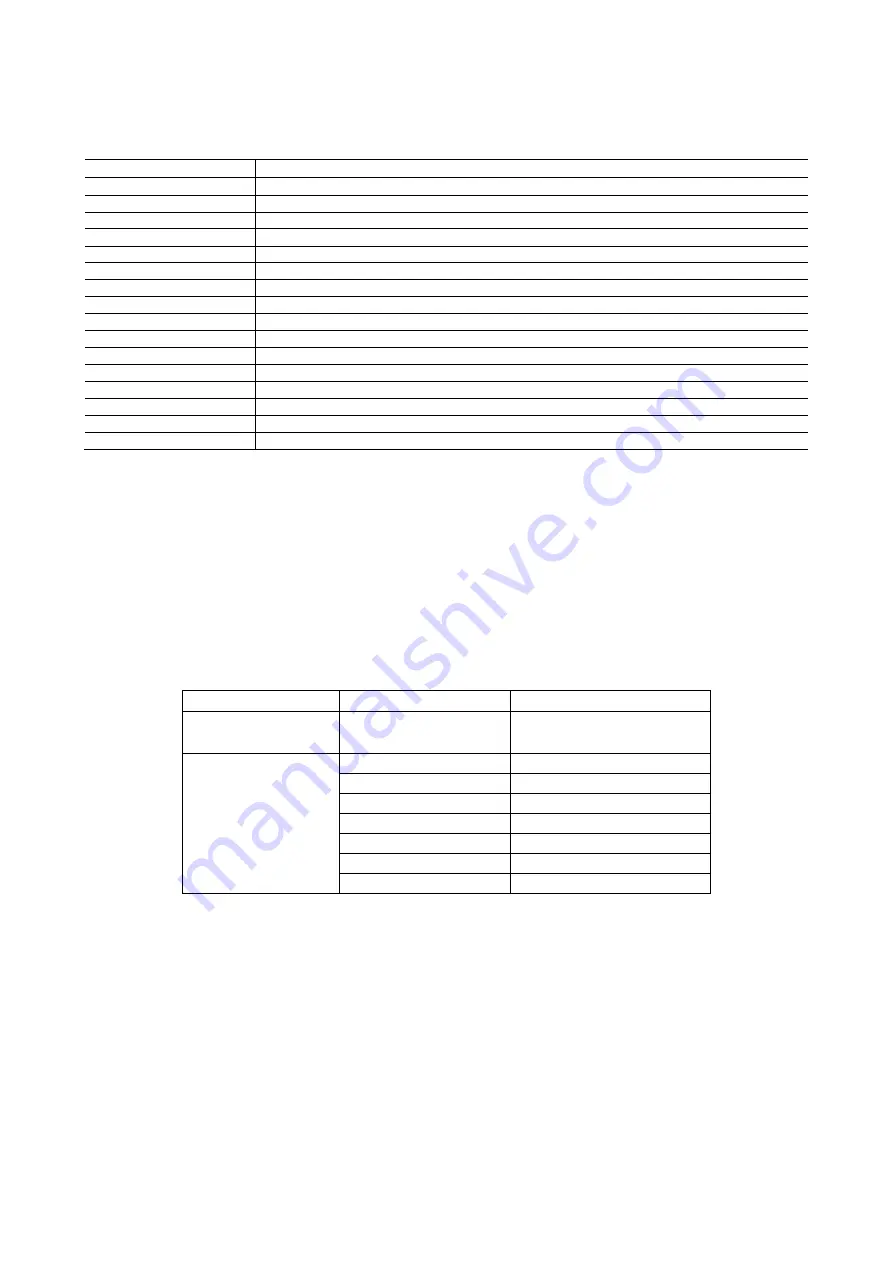

Table 61: Valid Configuration for audioif_sf[2:0] Address B8 (Main), Address 0x74[4:2]

audio_input_sel Value

audioif_sf Value Options

Corresponding Configuration

≠0b010

0b000

Not DSD Audio

0b011

0b001

DSD Audio, 64x32 kHz

0b010

DSD Audio, 64x44.1 kHz

0b011

DSD Audio, 64x48 kHz

0b100

DSD Audio, 64x88.2 kHz

0b101

DSD Audio, 64x96 kHz

0b110

DSD Audio, 64x176.4 kHz

0b111

DSD Audio, 64x192 kHz

6.11.2.4.

HBR Audio

The ADV8003 uses an HBR audio packet to transmit across the TMDS link compressed audio streams conforming to IEC 61937 and with

high bit rate (that is, bit rate higher than 6.144 Mbps).

The ADV8003 can be configured to receive an HBR stream by setting

to 0b011. The use of one or four input

stream(s) with or without biphase mark (BPM) encoding can be selected via the

field. Note that an audio master clock

input through the pin MCLK_IN is always required for the BPM encoding modes. For HBR mode, the audio sampling frequency must be

set via the

field.

can be toggled from 0 to 1 to synchronize the Pa and Pb syncword, which marks the beginning of a stream repetition with the

subpacket 0. For data bursts with a repetition period, which is a multiple of four frames, the synchronization will persist. If the data burst

does not have a repetition period of four frames, setting

is not needed but will not have any negative effects. The transition of

the bit from 0 to 1 causes the one time synchronization, so setting the bit from 1 to 0 will have no effect.

Summary of Contents for ADV8003

Page 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Page 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Page 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Page 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Page 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Page 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Page 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Page 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Page 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Page 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Page 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Page 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Page 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Page 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Page 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Page 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Page 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Page 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Page 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Page 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Page 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Page 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Page 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Page 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Page 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Page 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Page 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Page 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Page 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Page 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Page 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Page 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Page 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Page 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Page 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...