ADV8003 Hardware Manual

Rev. B, August 2013

46

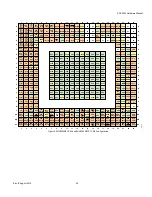

Table 4. ADV8003KBCZ-8C and ADV8003KBCZ-7C Pin Function Descriptions

Pin

No.

Mnemonic

Type

Description

A1

OSD_IN[23]/EXT_DIN[7

]

OSD video input/

miscellaneous

digital

External OSD Video Pixel Input Port (OSD_IN[23])/Additional TTL Input for

External CCIR 656 Video Data (EXT_DIN[7]).

A2

OSD_DE

OSD video sync

Data Enable for the OSD Input Port.

A3

OSD_CLK/EXT_CLK

OSD video sync

Pixel Clock for the OSD Input Port (OSD_CLK)/Pixel Clock for External Video Data

(EXT_CLK).

A4

AUD_IN[1]

Audio input

I

2

S0/DSD1 Audio Input.

A5

AUD_IN[2]

Audio input

I

2

S1/DSD2 Audio Input.

A6

AUD_IN[5]

Audio input

LRCLK/DSD5 Audio Input.

A7

ARC2_OUT

Audio output

Audio Return Channel for HDMI Tx2.

A8

MOSI1

Serial port control

Master Out Slave In (Serial Port 1). Serial Port 1 is used for OSD control.

A9

SCK2

Serial port control

Serial Clock (Serial Port 2). Serial Port 2 is used for the external flash ROM.

A10

CS2

Serial port control

Chip Select (Serial Port 2). Serial Port 2 is used for the external flash ROM.

A11

RESET

Miscellaneous

digital

Reset Pin for the ADV8003.

A12

XTALN

Miscellaneous

digital

Crystal Input.

A13

PVDD2

Power

PLL Digital Supply Voltage (1.8 V

).

A14

NC

No connect

Do not connect to this pin.

A15

NC

No connect

Do not connect to this pin.

A16

CVDD1

Power

Comparator Supply Voltage (1.8 V).

A17

RX_CN

Rx input

Rx Clock Complement Input.

A18

RX_0N

Rx input

Rx Channel 0 Complement Input.

A19

RX_1N

Rx input

Rx Channel 1 Complement Input.

A20

RX_2N

Rx input

Rx Channel 2 Complement Input.

A21

CVDD1

Power

Comparator Supply Voltage (1.8 V).

A22

NC

No connect

Do not connect to this pin.

A23

NC

No connect

Do not connect to this pin.

B1

OSD_IN[21]/EXT_DIN[5

]

OSD video input/

miscellaneous

digital

External OSD Video Pixel Input Port (OSD_IN[21])/Additional TTL Input for

External CCIR 656 Video Data (EXT_DIN[5]).

B2

OSD_IN[22]/EXT_DIN[6

]

OSD video input/

miscellaneous

digital

External OSD Video Pixel Input Port (OSD_IN[22])/Additional TTL Input for

External CCIR 656 Video Data (EXT_DIN[6]).

B3

OSD_VS

OSD video sync

Vertical Sync for the OSD Input Port.

B4

AUD_IN[0]

Audio input

S/PDIF/DSD0 Audio Input.

B5

AUD_IN[3]

Audio input

I

2

S2/DSD3 Audio Input.

B6

SFL

SFL

Subcarrier Frequency Lock Signal (SFL).

B7

ARC1_OUT

Audio output

Audio Return Channel for HDMI Tx1.

B8

MISO1

Serial port control

Master In Slave Out (Serial Port 1). Serial Port 1 is used for OSD control.

B9

MOSI2

Serial port control

Master Out Slave In (Serial Port 2). Serial Port 2 is used for the external flash ROM.

B10

MISO2

Serial port control

Master In Slave Out (Serial Port 2). Serial Port 2 is used for the external flash ROM.

B11

ALSB

I

2

C control

Sets LSB of ADV8003 I

2

C address (0x18 with LSB low, 0x1A with LSB high).

B12

XTALP

Miscellaneous

digital

ADV8003 Crystal Input.

B13

PVDD1

Power

PLL Analog Supply Voltage (1.8 V).

B14

NC

No connect

Do not connect to this pin.

B15

NC

No connect

Do not connect to this pin.

Summary of Contents for ADV8003

Page 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Page 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Page 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Page 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Page 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Page 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Page 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Page 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Page 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Page 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Page 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Page 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Page 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Page 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Page 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Page 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Page 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Page 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Page 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Page 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Page 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Page 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Page 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Page 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Page 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Page 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Page 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Page 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Page 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Page 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Page 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Page 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Page 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Page 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Page 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...