ADV8005 Hardware Reference Manual

UG-707

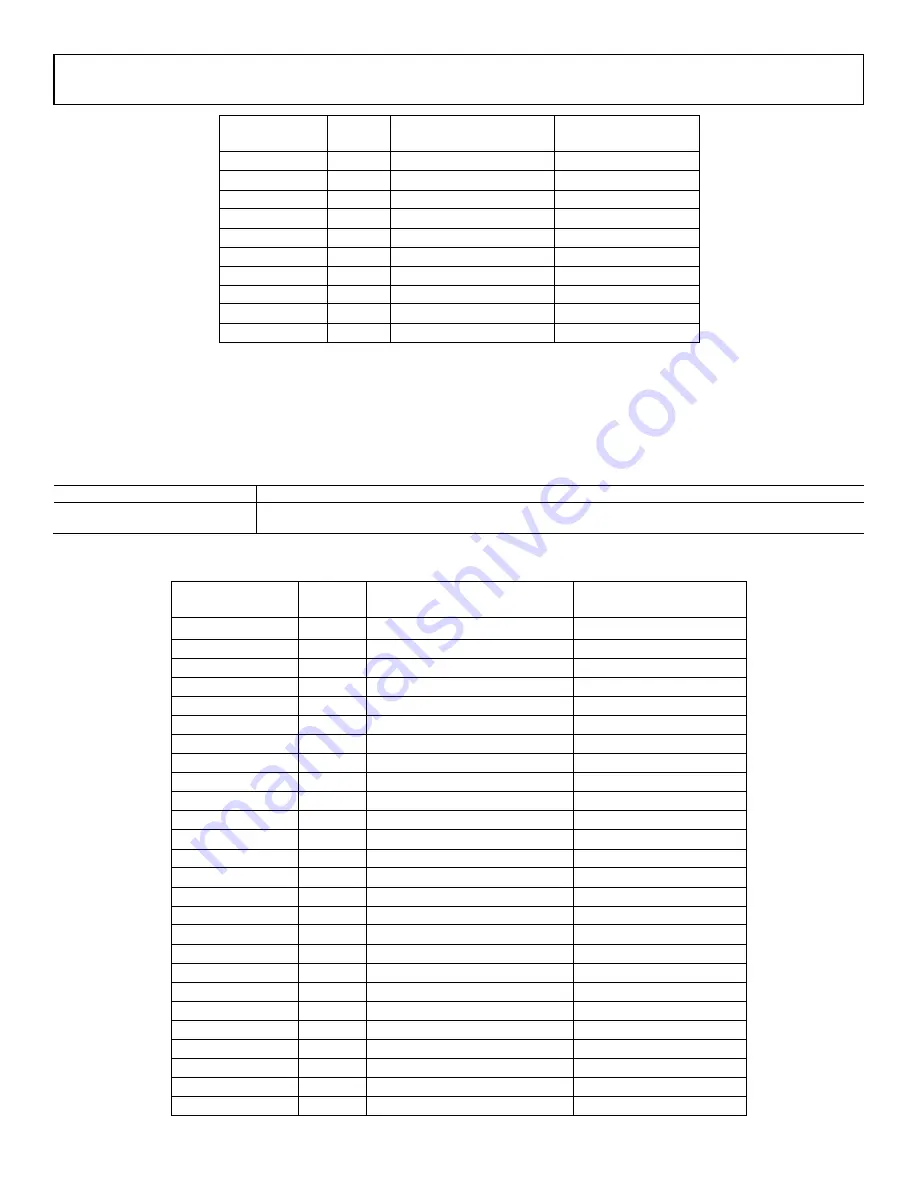

InfoFrame

Map Address

R/W

Register Name

Packet Byte No.

1

0x9E

R

isrc1_pb_0_19

PB18

0x9F

R

isrc1_pb_0_20

PB19

0xA0

R

isrc1_pb_0_21

PB20

0xA1

R

isrc1_pb_0_22

PB21

0xA2

R

isrc1_pb_0_23

PB22

0xA3

R

isrc1_pb_0_24

PB23

0xA4

R

isrc1_pb_0_25

PB24

0xA5

R

isrc1_pb_0_26

PB25

0xA6

R

isrc1_pb_0_27

PB26

0xA7

R

isrc1_pb_0_28

PB27

1

As defined by the HDMI 1.4 specifications

The ISRC1 packet registers are considered valid if the ISRC1 packet edge RAW interrupt is set to 1.

rx_isrc1_pckt_edge_raw

, IO Map,

Address 0x1AFB[4] (Read Only)

This readback indicates the raw status of the ISRC1 packet received signal. Once set this bit remains high until cleared via the corresponding

clear bit.

Function

rx_isrc1_pckt_edge_raw

Description

0 (default)

No new ISRC1 packet received

1

ISRC1 packet with new content received

Table 40: ISRC2 Packet Registers

InfoFrame

Map Address

R/W

Register Name

Packet Byte No.

1

0xE3F5

R/W

Packet Type Value

0x E3F6

R

isrc2_header1

HB1

0x E3F7

R

isrc2_header2

HB2

0x E3A8

R

isrc2_pb_0_1

PB0

0x E3A9

R

isrc2_pb_0_2

PB1

0x E3AA

R

isrc2_pb_0_3

PB2

0x E3AB

R

isrc2_pb_0_4

PB3

0x E3AC

R

isrc2_pb_0_5

PB4

0x E3AD

R

isrc2_pb_0_6

PB5

0x E3AE

R

isrc2_pb_0_7

PB6

0x E3AF

R

isrc2_pb_0_8

PB7

0x E3B0

R

isrc2_pb_0_9

PB8

0x E3B1

R

isrc2_pb_0_10

PB9

0x E3B2

R

isrc2_pb_0_11

PB10

0x E3B3

R

isrc2_pb_0_12

PB11

0x E3B4

R

isrc2_pb_0_13

PB12

0x E3B5

R

isrc2_pb_0_14

PB13

0x E3B6

R

isrc2_pb_0_15

PB14

0x E3B7

R

isrc2_pb_0_16

PB15

0x E3B8

R

isrc2_pb_0_17

PB16

0x E3B9

R

isrc2_pb_0_18

PB17

0x E3BA

R

isrc2_pb_0_19

PB18

0x E3BB

R

isrc2_pb_0_20

PB19

0x E3BC

R

isrc2_pb_0_21

PB20

0x E3BD

R

isrc2_pb_0_22

PB21

0x E3BE

R

isrc2_pb_0_23

PB22

Rev. A | Page 193 of 317