UG-707

ADV8005 Hardware Reference Manual

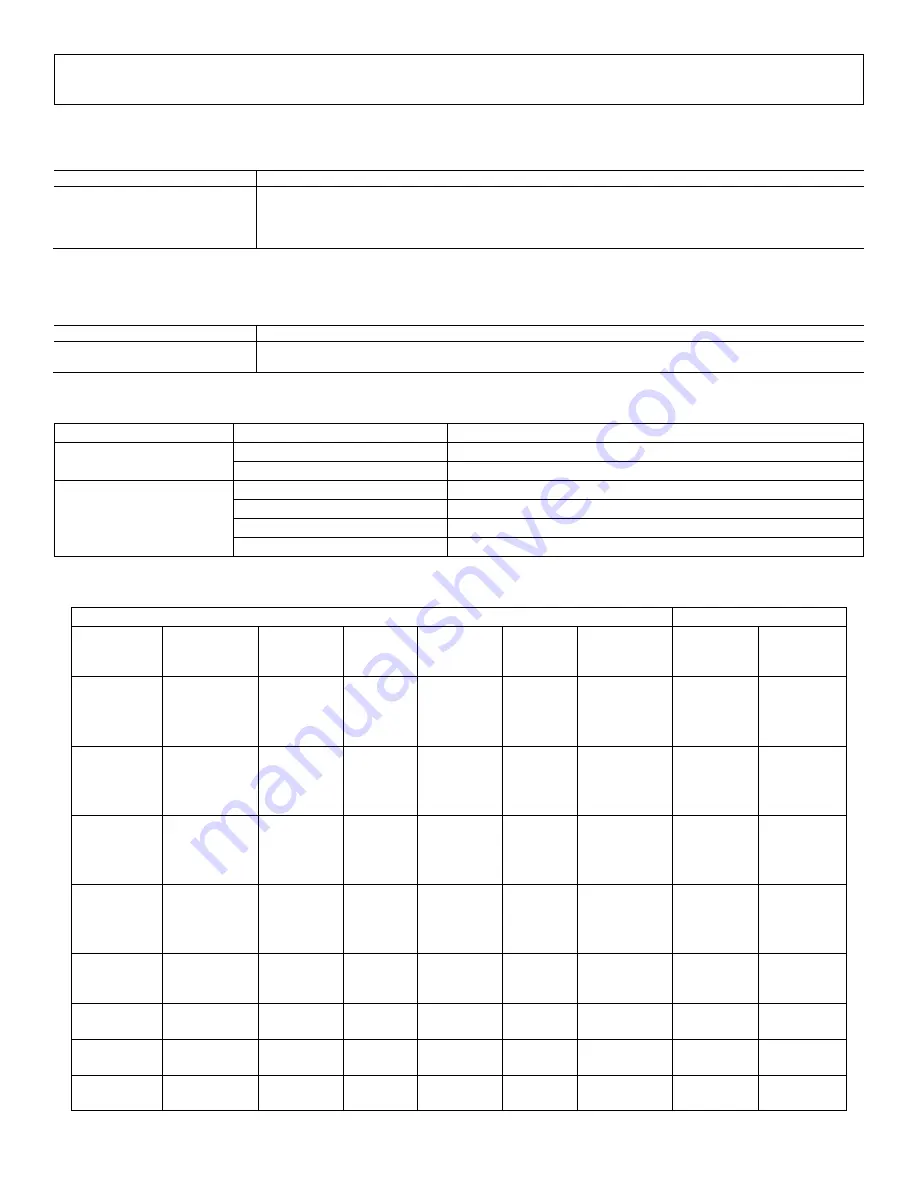

mclk_ratio[1:0]

, TX2 Main Map,

Address 0xF40A[1:0]

This signal is used to specify the ratio between the audio sampling frequency and the clock described using the N and CTS values.

Function

mclk_ratio[1:0]

Description

00

128*fs

01 (default)

256*fs

10

384*fs

11

512*fs

mclk_en

, TX2 Main Map,

Address 0xF40B[5]

This bit is used to select the audio master clock that is used by the audio block.

Function

mclk_en

Description

0 (default)

Use internally generated MCLK

1

Use external MCLK

Table 58: Valid Configuration for

audio_input_sel Value

audio_mode Value Options

Corresponding Configuration

0b010

0b0x

DSD in raw mode

0b1x

DSD in SDIF-3 mode

0b011

0b00

HBR input as 4 streams, with Bi-Phase Mark (BPM) encoding

0b01

HBR input as 4 stream, without BPM encoding

0b10

HBR input as 4 stream, without BPM encoding

0b11

HBR input as 1 stream, without BPM encoding

Table 59: Audio Input Format Summary

Input

Output

audio_input

_sel Value

audio_mode

Value

I2s_format

Value

Audio

Input

Signal

Clock Pins

Encoding

Input Pin

Mapping

Format

Packet Type

0b000

0bXX

0b00

I2S[3:0]

SCLK,

LRCLK,

MCLK

1

Normal

AUD_IN[4:0]

AUD_IN[5]

SCLK

MCLK

Standard

I2S

Audio

Sample

Packet

0b000

0bXX

0b01

I2S[3:0]

SCLK,

LRCLK,

MCLK

1

Normal

AUD_IN[4:0]

AUD_IN[5]

SCLK

MCLK

Right

justified

Audio

Sample

Packet

0b000

0bXX

0b10

I2S[3:0]

SCLK,

LRCLK,

MCLK

1

Normal

AUD_IN[4:0]

AUD_IN[5]

SCLK

MCLK

Left justified Audio

Sample

Packet

0b000

0bXX

0b11

I2S[3:0]

SCLK,

LRCLK,

MCLK

1

Normal

AUD_IN[4:0]

AUD_IN[5]

SCLK

MCLK

AES3 direct

Audio

Sample

Packet

0b001

0b00

0bXX

SPDIF

MCLK

1

Biphase

Mark

AUD_IN[0]

MCLK

IEC60958 or

IEC61937

Audio

Sample

Packet

0b010

0b1X

0bXX

DSD[5:0]

SCLK

Normal

AUD_IN[5:0]

SCLK

DSD

DSD Packet

0b010

0b1X

0bXX

DSD[5:0]]

SCLK

SDIF-3

AUD_IN[5:0]

SCLK

DSD

DSD Packet

0b011

0b00

0bXX

I2S[3:0]

MCLK

Biphase

Mark

AUD_IN[4:0]

MCLK

IEC61937

HBR Packet

Rev. A | Page 214 of 317