UG-707

ADV8005 Hardware Reference Manual

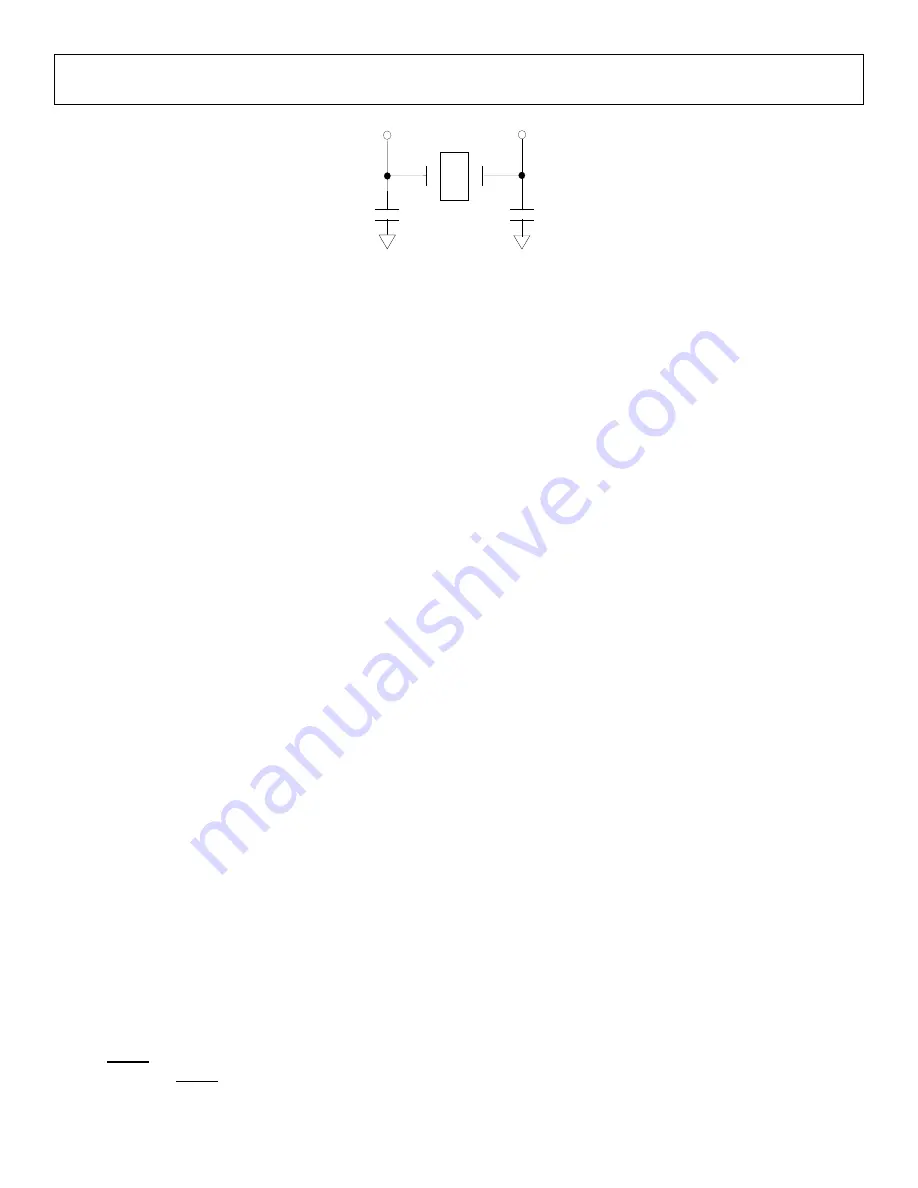

Figure 144: Crystal Circuit

These guidelines are followed to ensure correct operation:

•

Use the correct frequency crystal (27 MHz recommended). Tolerance should be 50 ppm or better.

•

Know the C

load

for the crystal part number selected. The value of capacitors C1 and C2 must be matched to the C

load

for the specific

crystal part number in the user’s system.

To find C1 and C2, use the following formula:

C1

=

C2

=

2(C

load

– C

stray

)

-

C

pg

where

C

stray

is usually 2 to 3 pF, depending on board traces and

C

pg

(pin-to-ground-capacitance) is 4 pF for the

Example:

C

load

= 30 pF,

C1

= 50 pF,

C2

= 50 pF (in this case, 47 pF is the nearest real-life cap value to 50 pF)

Encoder Component Placement

External component placement must be carefully considered – they should be kept as far away from noisy circuits as possible, as close to the

as possible and preferably on the same layer as the

. The external loop filter (connected to PVDD3), COMP, termination

resistors, V

REF

, and R

SETx

circuits must all be laid out carefully otherwise noise may couple onto the SD or HD encoder outputs.

Any external filter and buffer components connected to the encoder analog outputs should be placed close to the

possibility of noise cross talk between neighboring circuitry. The encoder analog output traces should be kept as short as possible to reduce the

possibility of any signal integrity issues and to minimize the effect of trace capacitance on output bandwidth.

HDMI Transmitter Component Placement

External component placement must be carefully considered – they should be kept as far away as possible from noisy circuits, as close to the

as possible and preferably on the same layer as the

. The R_TX1 and R_TX2 resistors and PVDD5 and PVDD6 power

supplies must all be carefully laid out otherwise the HDMI transmitter performance, for example, HDMI compliance testing, may be reduced.

Power Supply Design and Sequencing

The

requires only two regulators, one 3.3 V and one 1.8 V. The recommended power supply design is illustrated in

If using more than one 1.8 V regulator to supply

, it must be ensured that DVDD_DDR, PVDD_DDR and DVDD are supplied by the

same regulator.

The power-up sequence of the

is as follows:

1.

Hold RESET and PDN pins low.

2.

Bring up the 3.3 V supplies (DVDD_IO, AVDD1, and AVDD2).

3.

A delay of a minimum of 20 ms is required from the point in which the 3.3 V reaches its minimum recommended value (that is, 3.14 V)

before powering up the 1.8 V supplies.

4.

Bring up the 1.8 V supplies (DVDD, CVDD1, PVDD1, PVDD2, PVDD3, AVDD3, DVDD_DDR, and PVDD_DDR). These should be

powered up together, that is, there should be a difference of less than 0.3 V between them.

5.

RESET may be pulled high after supplies have been powered up.

6.

A complete RESET is recommended after power up. This can be performed by the system microcontroller.

47pF

X

T

A

L

27MHz

C1

C2

47pF

Rev. A | Page 290 of 317