UG-1882

Rev. 0 | Page 4 of 28

EVALUATION BOARD HARDWARE GUIDE

IN0

COM

IN1

CS

AD4696

160-PIN FMC

OR

12-PIN PMOD

+3.3V

–2.5V

+12V

V

REF

REFERENCE

BUFFER

POWER MANAGEMENT CIRCUITRY

REFERENCE

ON-BOARD

DC BIAS

CHANNEL 2

TO

CHANNEL 15

CNV

SDI

SCK

SDO

BSY_ALT_GP0

RESET

IN14

IN15

+1.8V

+5V

+7.5V

8-LEAD MSOP

DUAL OP AMPS

R

R

V

REF

REF

SM

A

CO

NNE

C

T

O

RS

CH0

AND CH1

V

REF

/2

25058-

002

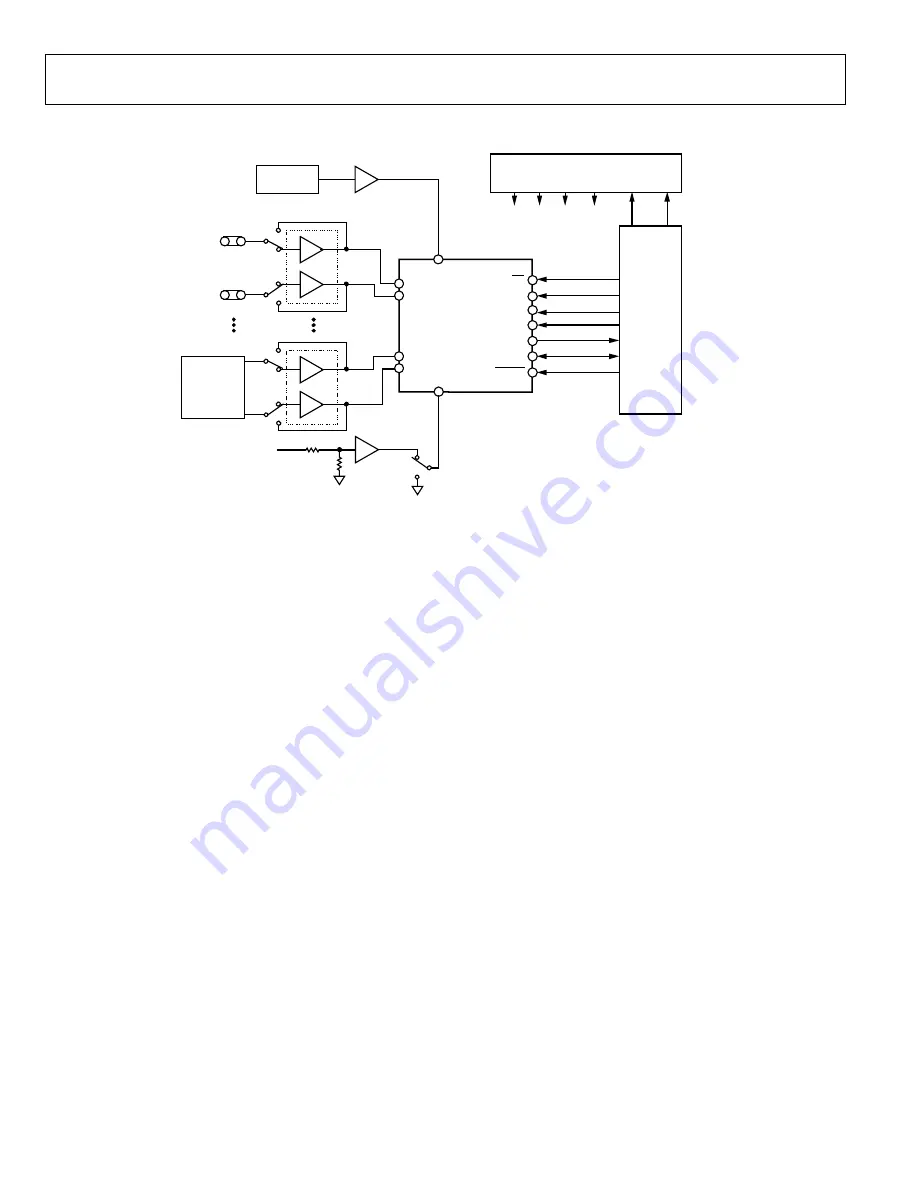

Figure 2. EVAL-AD4696FMCZ Simplified Block Diagram

HARDWARE OVERVIEW

Figure 2 shows a simplified block diagram of the EVAL-

AD4696FMCZ hardware. This evaluation board features the

and peripheral circuitry required for evaluating the

device.

The EVAL-AD4696FMCZ is a quick start evaluation platform that

showcases the performance of the AD4696 with no or minimal

modifications required. Figure 24 to Figure 30 contain the EVAL-

AD4696FMCZ schematics. The evaluation board includes an

on-board 5 V reference, an ADC driver amplifier for all 16

AD4696 channels, the ability to configure driver amplifiers on

Channel IN0 and Channel IN1 in many common configurations,

and configurable dc voltage levels for the IN2 through the IN15

channels. By default, the EVAL-AD4696FMCZ is powered entirely

from the FMC connector supplies. The Analog Front-End section,

the Reference section, the Power Supplies section, and the

Digital Interface section describe the design of each of these

circuit blocks, how they are used to evaluate the AD4696, and

common hardware modifications for each.

ANALOG FRONT-END

The EVAL-AD4696FMCZ evaluation hardware includes an

ADC driver amplifier for each of the 16 analog inputs (IN0 to

IN15). The driver amplifiers (

and seven

devices to drive IN2 and IN15) come in a

common dual-amplifier, 8-lead MSOP package, which allows

multiple ADC driver options to be evaluated with the AD4696

on the EVAL-AD4696FMCZ.

Channel IN0 and Channel IN1 have been configured to

demonstrate ac performance of the AD4696, whereas Channel

IN2 through Channel IN15 have been configured to demonstrate

simple noise measurements and signal settling measurements

with dc voltages generated on board. The amplifiers driving

Channel IN0 and Channel IN1 can be configured to perform

common signal conditioning functions by adding specific passive

components (see the Evaluating AD4696 AC Performance section).

The amplifiers driving Channel IN2 to Channel IN15 are driven

to dc voltages by on-board amplifiers and user configurable

resistor dividers (see the Configuring DC Channels (IN2

Through IN15) section).

Evaluating AD4696 AC Performance (IN0 and IN1)

The EVAL-AD4696FMCZ hardware includes two channels for

evaluating the ac performance of the AD4696 using a precision

ac signal generator.

Component A0 includes two amplifiers that function as the

ADC drivers for the AD4696 IN0 and IN1 inputs. By default,

A0 is populated with the ADA4805-2 due to its low noise and low

distortion that makes it suitable for ac performance evaluation.

The Subminiature Version A (SMA) connectors, J1 through J4,

are routed to the inputs of A0 via the signals labeled CH0 and

CH1 in Figure 24 and Figure 26.

The J1 through J4 SMA connectors are shown in Figure 24. To

apply an ac signal to the IN0 channel, connect the ac signal

generator output to J1 or J3. Likewise, to apply an ac signal to

the IN1 channel, connect the ac signal generator output to J2 or

J4. The ac signal generator must have similar or lower noise and

distortion specifications to the AD4696 to properly evaluate

AD4696 ac performance (see the AD4696 data sheet for

AD4696 device specifications).

The IN0 and IN1 channel amplifiers in A0 can be configured to

implement common feedback topologies including a unity-gain

buffer, non inverting or inverting amplifier, and active filters, by

populating the surrounding passive components appropriately