EVAL-AD5340DBZ User Guide

UG-981

Rev. 0 | Page 7 of 13

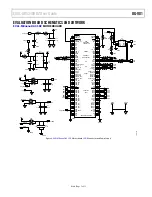

EVALUATION BOARD SCHEMATICS AND ARTWORK

EVAL-MBnanoDAC-SDZ

MOTHERBOARD

Figure 8.

EVAL-MBnanoDAC-SDZ

Motherboard

SDP-B

Connector and Power Supply

EXT_VDD

VLOGIC

GND

EXT_VSS

SDP

STANDARD

CONNECTOR

PARALLEL

PORT

SPORT

SPI

I2C

GENERAL

INPUT/OUTPUT

TIMERS

*NC ON BLACKFIN SDP

120

NC

119

NC

118

GND

117

GND

116

VIO(+3.3V)

115

GND

114

PAR_D22*

113

PAR_D20*

112

PAR_D18*

111

PAR_D16*

110

PAR_D15

109

GND

108

PAR_D12

107

PAR_D10

106

PAR_D8

105

PAR_D6

104

GND

103

PAR_D4

102

PAR_D2

101

PAR_D0

100

PAR_WR

99

PAR_INT

98

GND

97

PAR_A2

96

PAR_A0

95

PAR_FS2

94

PAR_CLK

93

GND

92

SPORT_RSCLK

91

SPORT_DR0

90

SPORT_RFS

89

SPORT_TFS

88

SPORT_DT0

87

SPORT_TSCLK

86

GND

85

SPI_SEL_A

84

SPI_MOSI

83

SPI_MISO

82

SPI_CLK

81

GND

80

SDA_0

79

SCL_0

78

GPIO1

77

GPIO3

76

GPIO5

75

GND

74

GPIO7

73

TMR_B

72

TMR_D

71

CLK_OUT

70

NC

69

GND

68

NC

67

NC

66

NC

65

WAKE

64

SLEEP

63

GND

62

UART_TX

61

BMODE1

60

RESET_IN

59

UART_RX

58

GND

57

RESET_OUT

56

EEPROM_A0

55

NC

54

NC

53

NC

52

GND

51

NC

50

NC

49

TMR_C*

48

TMR_A

47

GPIO6

46

GND

45

GPIO4

44

GPIO2

43

GPIO0

42

SCL_1

41

SDA_1

40

GND

39

SPI_SEL1/SPI_SS

38

SPI_SEL_C

37

SPI_SEL_B

36

GND

35

SPORT_INT

34

SPI_D3*

33

SPI_D2*

32

SPORT_DT1

31

SPORT_DR1

30

SPORT1_TDV*

29

SPORT0_TDV*

28

GND

27

PAR_FS1

26

PAR_FS3

25

PAR_A1

24

PAR_A3

23

GND

22

PAR_CS

21

PAR_RD

20

PAR_D1

19

PAR_D3

18

PAR_D5

17

GND

16

PAR_D7

15

PAR_D9

14

PAR_D11

13

PAR_D13

12

PAR_D14

11

GND

10

PAR_D17*

9

PAR_D19*

8

PAR_D21*

7

PAR_D23*

6

GND

5

USB_VBUS

4

GND

3

GND

2

NC

1

VIN

J10

1

A0

2

A1

3

A2

4

VSS

8

VCC

7

WP

6

SCL

5

SDA

U3

24LC32

R2

100kΩ

R3

100kΩ

R4

DNP

DGND

AGND

L1

BEAD

R1

1.6Ω

+

C11

4.7µF

C10

0.1µF

+

C7

10µF

1

2

3

4

5

U2

ADP121-AUJZ33

C3

1µF

C4

1µF

C

B

A

LK5

J6-1

J6-2

C5

0.1µF

+

C6

10µF

A

B

LK6

J5-1

J5-2

J5-3

C2

0.1µF

+

C1

10µF

A

B

LK7

R7

100Ω

R5

100Ω

R6

100Ω

R8

100Ω

R9

100Ω

R10

100Ω

R11

100Ω

R12

100Ω

R13

100Ω

R14

100Ω

C8

0.1µF

+

C9

10µF

R15

100Ω

R16

DNP

PD

GAIN

SCL

SDA

CS

WR

DB0

DB2

DB4

DB6

DB8

DB10

DB1

DB3

DB5

DB7

DB9

DB11

+3.3V

+3.3V

DGND

+5V

USB_VBUS

USB_VBUS

+3.3V

VDD

+3.3V

DGND

VLOGIC

DGND

+3.3V

DGND

DGND

VSS

+5V

CLR

LDAC

SCLK

SDO

SDIN

SYNC

EXT_VDD

EXT_VDD

+5V

DGND

DGND

DGND

DGND

DGND

DGND

14516-

008

VIN

GND

EN

NC

VOUT