EVAL-ADuC7026 User Guide

UG-669

Rev. B | Page 3 of 16

GETTING STARTED WITH THE EVALUATION HARDWARE

POWER SUPPLY

Connect the 9 V power supply via the 2.1 mm input power

socket (J5). The input connector is configured as a center

negative, that is, as GND on the center pin and +9 V on the

outer shield.

The 9 V supply is regulated via the Linear Voltage Regulator U5.

The 3.3 V regulator output is used to drive the digital side of the

board directly. The 3.3 V supply is also filtered and then used to

supply the analog side of the board.

When on, the LED (D3) indicates that a valid 3.3 V supply is

being driven from the regulator circuit. All active components

are decoupled with 0.1 µF at device supply pins to ground.

RS-232 INTERFACE

The

(U1) P1.1 and P1.0 lines are connected to the

RS-232 interface cable via Connector J1. The interface cable

generates the required level shifting to allow direct connection

to a PC serial port. Ensure that the cable supplied is connected

to the board correctly, that is, DVDD is connected to DVDD

and DGND is connected to DGND.

EMULATION INTERFACE

Nonintrusive emulation and download are possible on the

, via JTAG, by connecting a JTAG emulator to the

J4 connector.

CRYSTAL CIRCUIT

The board is fitted with a 32.768 kHz crystal, from which the

on-chip PLL circuit can generate a 41.78 MHz clock.

EXTERNAL REFERENCE (

)

The external 2.5 V Reference Chip U2 has two functions. It is

provided on the evaluation board to demonstrate the external

reference option of the

to generate the V

OCM

voltage of the differential amplifier if

required.

RESET/DOWNLOAD/IRQ0 PUSH-BUTTONS

A reset push-button is provided to allow the user to reset the

part manually. When the button is pushed, the reset pin of the

is pulled to DGND. Because the reset pin on the

is Schmidt triggered internally, there is no need to

use an external Schmidt trigger on this pin.

When pushed, the IRQ0 push-button switch drives P0.4/IRQ0

high. This can be used to initiate an external interrupt 0.

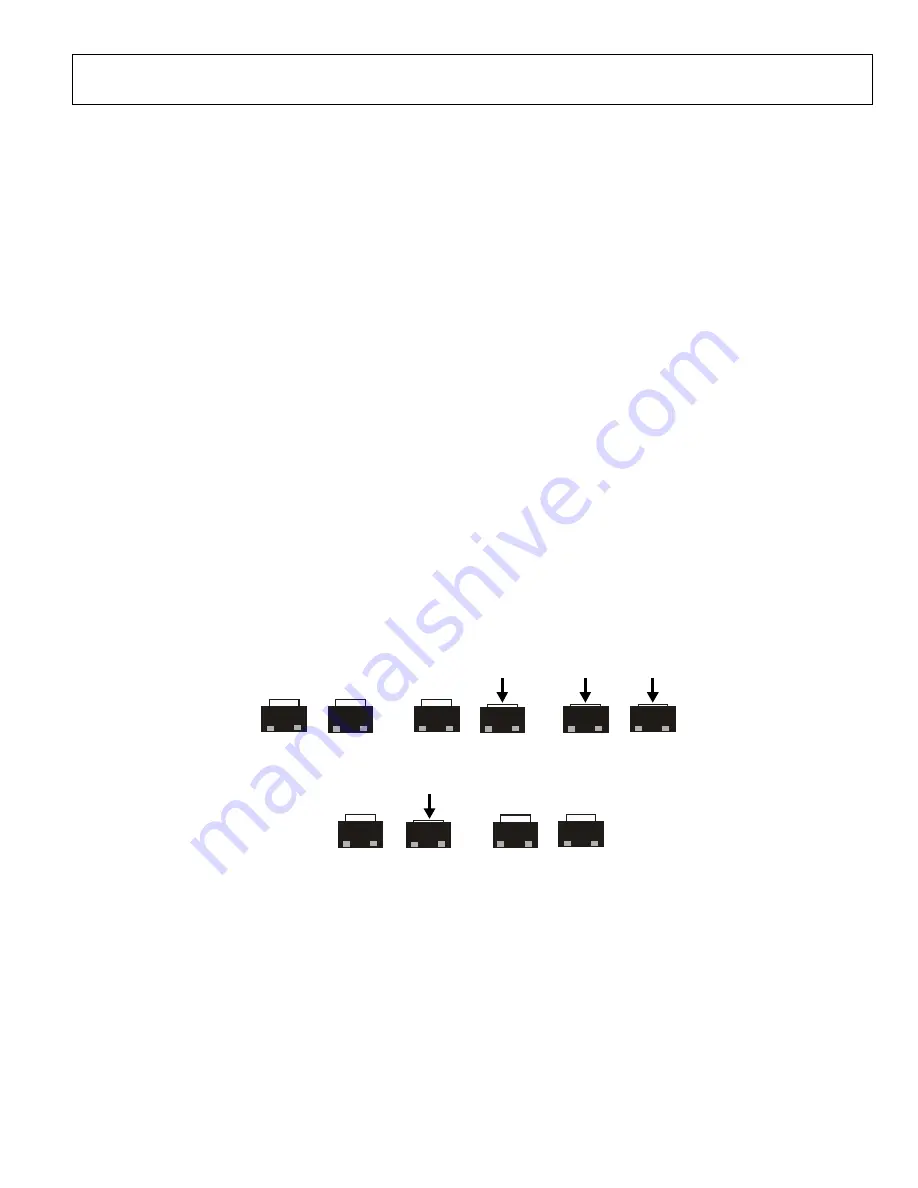

To enter serial download mode, the user must pull the P0.0/BM

pin low while reset is toggled. On the evaluation board, serial

download mode can easily be initiated by holding down the

serial download push-button (S2) while inserting and releasing

the reset button (S3) as shown in Figure 2.

S3

(RESET = 1)

S2

(BM = 1)

(A) S3 AND S2 RELEASED

S2

(BM = 0)

S3

(RESET = 1)

(B) PUSH S2

S3

(RESET = 1)

S2

(BM = 0)

(D) RELEASE S3

S2

(BM = 0)

S3

(RESET = 0)

(C) PUSH S3

S2

(BM = 1)

S3

(RESET = 1)

(E) RELEASE S2

05032-

001

Figure 2. Entering Serial Download Mode on the Evaluation Board