HSC-ADC-EVALC

Rev. 0 | Page 23 of 32

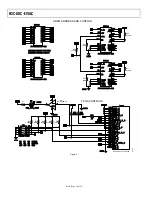

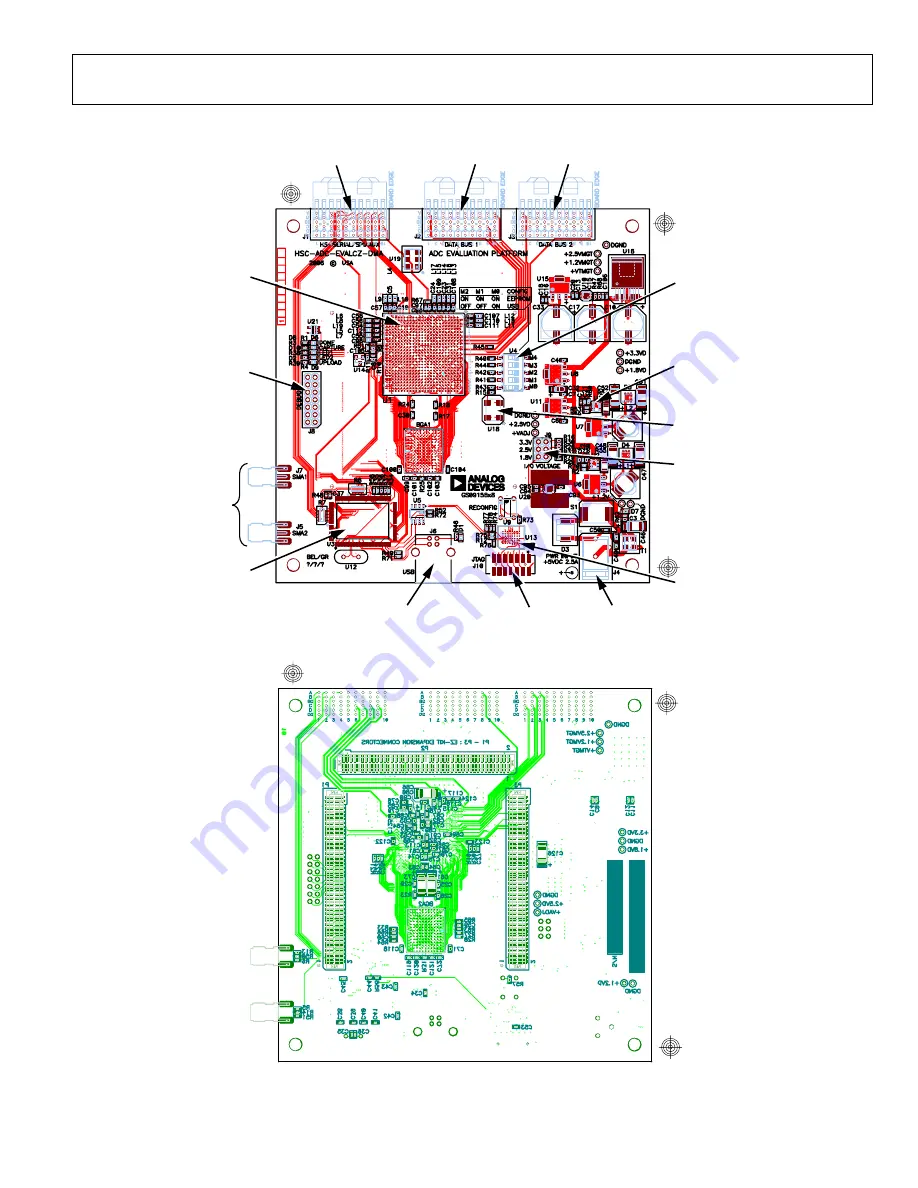

PCB LAYOUT

06

67

6-

0

19

GENERAL PURPOSE I/O,

USB/SPI CONTROL

DATA BUS 1

DATA BUS 2

XILINX

VIRTEX-4

FPGA

DEBUG

PINS

EXTERNAL

SYNC I/O

CYPRESS USB

CONTROLLER

USB CONNECTOR

FPGA JTAG

CONNECTOR

5VDC POWER

INPUT

FPGA LOAD

SELECT

ON BOARD

POWER SUPPLY

100MHz

OSCILLATOR

FPGA I/O

VOLTAGE MODE

FPGA CONFIG

PROM

Figure 19. Top Silkscreen

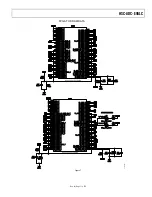

06

67

6-

02

0

Figure 20. Bottom Silkscreen