HSC-ADC-EVALC

Rev. 0 | Page 5 of 32

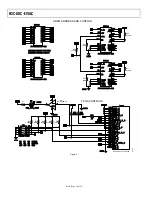

ROHDE & SCHWARZ,

SMHU,

2V p-p SIGNAL

SYNTHESIZER

ROHDE & SCHWARZ,

SMHU,

2V p-p SIGNAL

SYNTHESIZER

BAND-PASS

FILTER

USB

CONNECTION

06

67

6-

004

HSC-ADC-EVALC

DATA CAPTURE

BOARD

PC

RUNNING

VisualAnalog

–

+

PS

GN

D

V

RE

G

5V DC

3A MAX

WALL OUTLET

100V TO 240V AC

47Hz TO 63Hz

DATA BUS 2

PARALLEL

LVDS/CMOS

OUTPUTS

EVALUATION

BOARD

DATA BUS 1

PARALLEL

LVDS/CMOS

OUTPUTS

XFMR

INPUT

CLK

SWITCHING

POWER

SUPPLY

SPI

SPI

ONBOARD POWER

SUPPLY

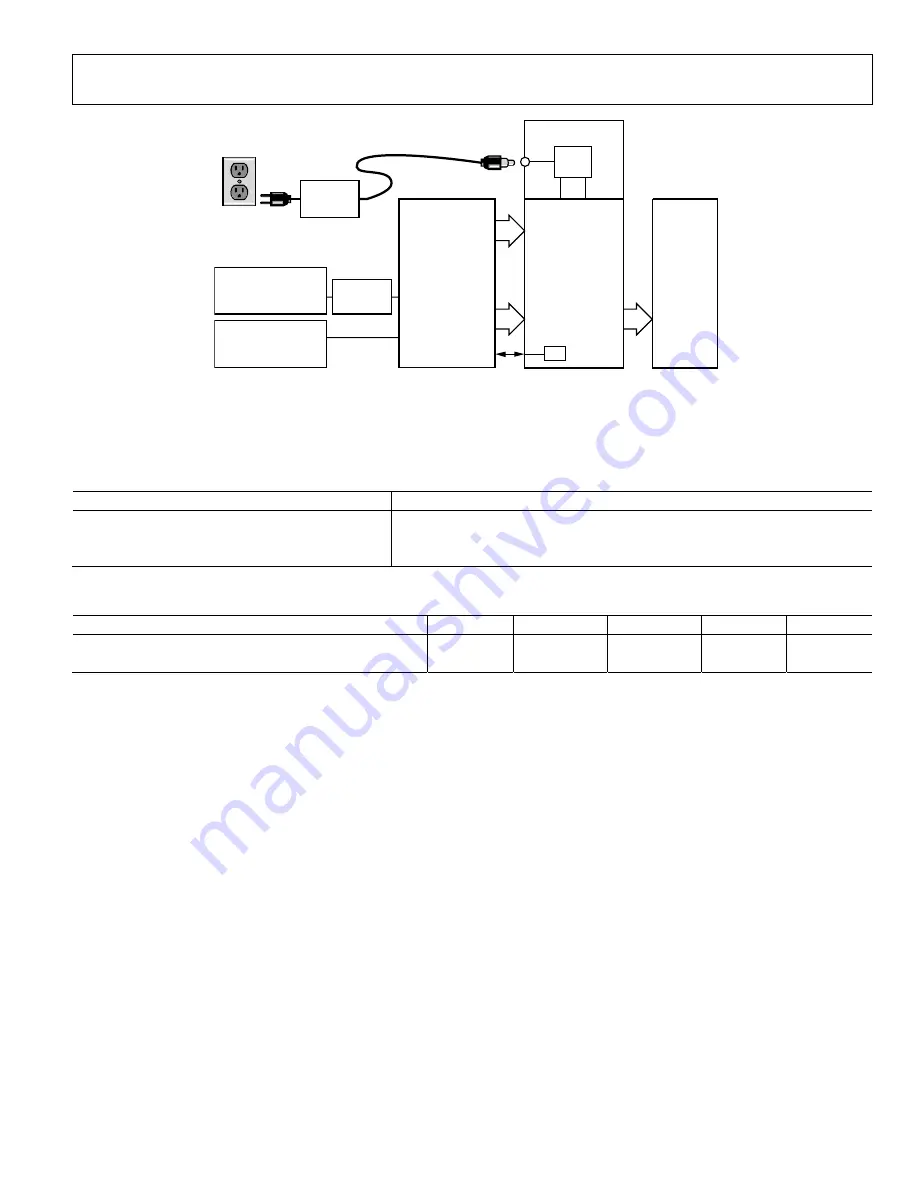

Figure 2. Example Setup Using ADC Evaluation Board and HSC-ADC-EVALC ADC Capture Board

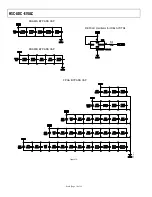

JUMPERS

Default Settings

Table 1 lists the default settings for the HSC-ADC-EVALC evaluation kit.

Table 1. Jumper Configurations

Jumper Number

Description

J9, Pin 1 to Pin 2 (1.8 V)

Default. Sets FPGA I/O voltage to 1.8 V logic (hardwired, do not remove).

J9, Pin 3 to Pin 4 (2.5 V)

Install single jumper here to set FPGA I/O voltage to 2.5 V logic.

J9, Pin 5 to Pin 6 (3.3 V)

Install single jumper here to set FPGA I/O voltage to 3.3 V logic.

Table 2. FPGA Configuration Mode

U4 DIP Switch Setting

M0

M1

M2

M3

M4

FPGA Configured via EEPROM

On

On

On

Reserved

Reserved

FPGA Configured via USB (Default)

On

Off

Off

Reserved

Reserved