ezTrainer

User Manual

FPGA MADE eAzY

All Rights Reserved

Anaya Tech Systems Pvt Ltd

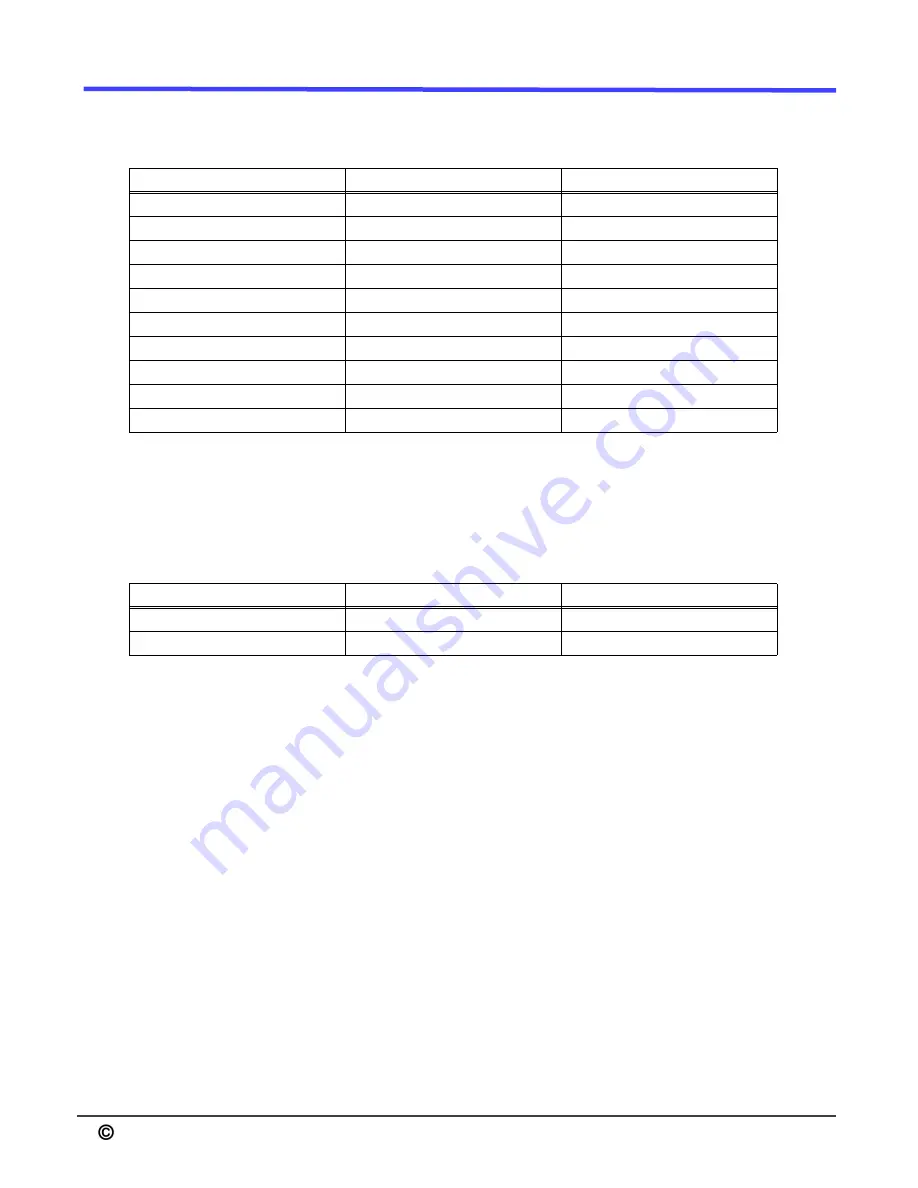

5.4 UART INTERFACE

A RS-232 transceiver is connected to the FPGA pins as shown in the table below. See datasheet of the

transceiver at www.maxim-ic.com.

5.5 AUDIO INTERFACE

A mono audio codec TLV320AIC1106 from texas instruments (www.ti.com) is connected to the FPGA to

provide an audio interface. 13-bit Linear as well as 9-bit u-law digital audio data is sent over the PCM interface

to the audio codec, which is then played over the speaker. Audio can also be captured over the MIC and sent

back to FPGA over PCM. Speaker Mute and code selection can be done through the jumpers JP301/300, see

below:

A11

42

35

A12

41

36

BA0

40

20

BA1

39

21

CS

34

19

CAS

36

17

RAS

33

18

WE

30

16

CKE

35

37

CLK

31

38

Table 4:

Signal Names

FPGA Pin

MAX3221 pin

T1N

178

11

R1OUT

175

9

Table 3:

Signal Names

FPGA Pin

SDRAM pin