2192-12132-000-000

*

More details of the internal registers are in the Intel Developer Manual on the Development Kit

CD.

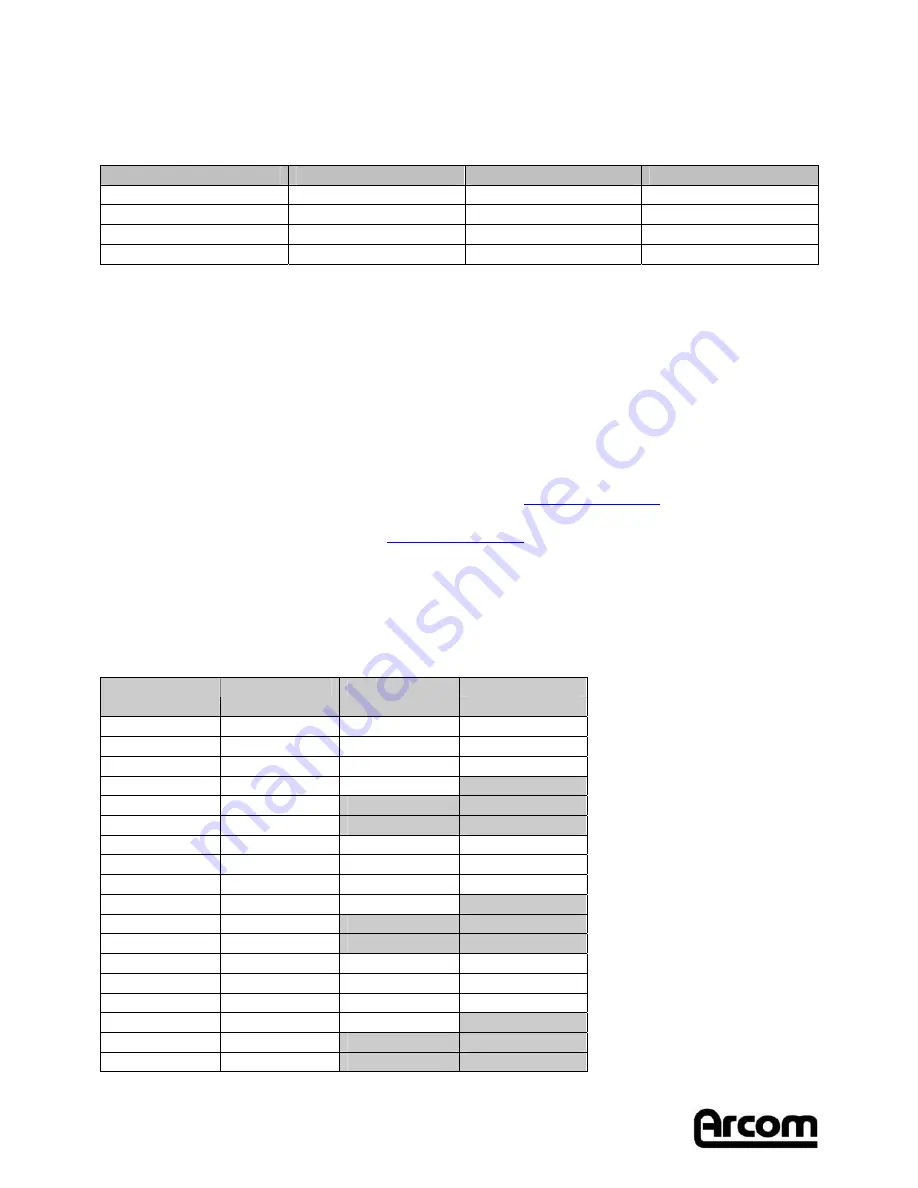

The following table shows the translations made by the MMU under RedBoot:

Device

Size

Physical

Virtual

Boot Rom (CS0)

1MByte

0x0

0x5000 0000

SDRAM 64MByte

0xA000

0000

0x0

Flash Array

64MByte

0x0400 0000

0x6000 0000

Cache Flush

128MByte

N/A

0xE000 0000

Ethernet, USB, SRAM, UARTs, CompactFlash, PC104 and all internal registers are the physical

address location.

Graphics Controller

The Intel PXA255 processor contains a 16-bit flat panel display controller and provides an

interface capable of driving passive (STN) or active (TFT) flat panel displays. A full explanation

of the graphics controller operation can be found in the PXA255 data sheets included on the

support CD. The flat panel data and control signals are routed to a 40-way high-density

connector (PL3). The flat panel interface can be configured to drive a variety of panel types.

The part number for the flat panel interface connector is:

Oupiin 3214-40RB

The mating connector is part number:

Oupiin 1203-40GB

The VIPER-FPIF is available which allows the user to easily wire-up a new panel using pin and

crimp style connectors.

The following tables provide a cross-reference between the flat panel output signals and their

function when configured for different displays.

9-Bit TFT

Panel Data

Bus Bit

18-Bit TFT

12-Bit TFT

FPD 15

R5

R3

R2

FPD 14

R4

R2

R1

FPD 13

R3

R1

R0

FPD 12

R2

R0

FPD 11

R1

GND

R0

FPD 10

G5

G3

G2

FPD 9

G4

G2

G1

FPD 8

G3

G1

G0

FPD 7

G2

G0

FPD 6

G1

FPD 5

G0

FPD 4

B5

B3

B2

FPD 3

B4

B2

B1

FPD 2

B3

B1

B0

FPD 1

B2

B0

FPD 0

B1

GND

B0

Page 18