Introduction

1-2

Copyright © ARM Limited 2000. All rights reserved.

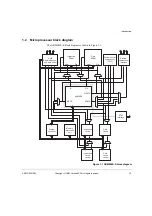

1.1

About the ARM946E-S

The ARM946E-S is a synthesizable macrocell combining an ARM processor. It is a

member of the ARM9 Thumb family of high-performance, 32-bit system-on-chip

processor solutions.

The ARM946E-S has tightly-coupled SRAM memory, and instruction and data caches

and is targeted at a wide range of embedded applications where high-performance, low

system cost, small die size and low power are all important.

The ARM946E-S processor macrocell is a Harvard architecture cached processor that

provides a complete high-performance processor subsystem, including:

•

An ARM9E-S RISC integer CPU core featuring:

—

ARMv5TExP 32-bit instruction set with improved ARM/Thumb code

interworking and enhanced multiplier designed for improved DSP

performance.

—

ARM debug architecture with additional support for real-time debug. This

allows critical exception handlers to execute while debugging the system.

•

Tightly-coupled SRAM for each of the instruction and data CPU interfaces. The

size of both the instruction and data SRAM are implementor-configurable.

•

Instruction and data caches. The design can be easily modified to allow any

combination of caches from 4 Kbytes to 1 Mbyte.

•

A protection unit that allows the memory to be segmented and protected in a

simple manner, ideal for embedded control applications.

•

An AMBA AHB bus interface. ARM946E-S interfaces to the rest of the system

are through use of unified address and data buses. This interface is compatible

with the AMBA AHB bus standard.

•

Support for external coprocessors allowing floating point or other application

specific hardware acceleration to be added. For coprocessor support, the

instruction and data buses are exported along with simple handshaking signals.

•

Support for the use of a scan test methodology for the standard cell logic and

Built-In-Self-Test (BIST) for the tightly-coupled SRAM and caches.

•

An interface to an external Embedded Trace Macrocell (ETM) to support

real-time tracing of instructions and data.

Providing this complete high frequency subsystem frees the system-on-a-chip designer

to concentrate on design issues unique to their system. The synthesizable nature of the

device eases integration into ASIC technologies.

Summary of Contents for ARM946E-S

Page 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Page 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Page 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...