Direct Memory Access (DMA)

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

5-9

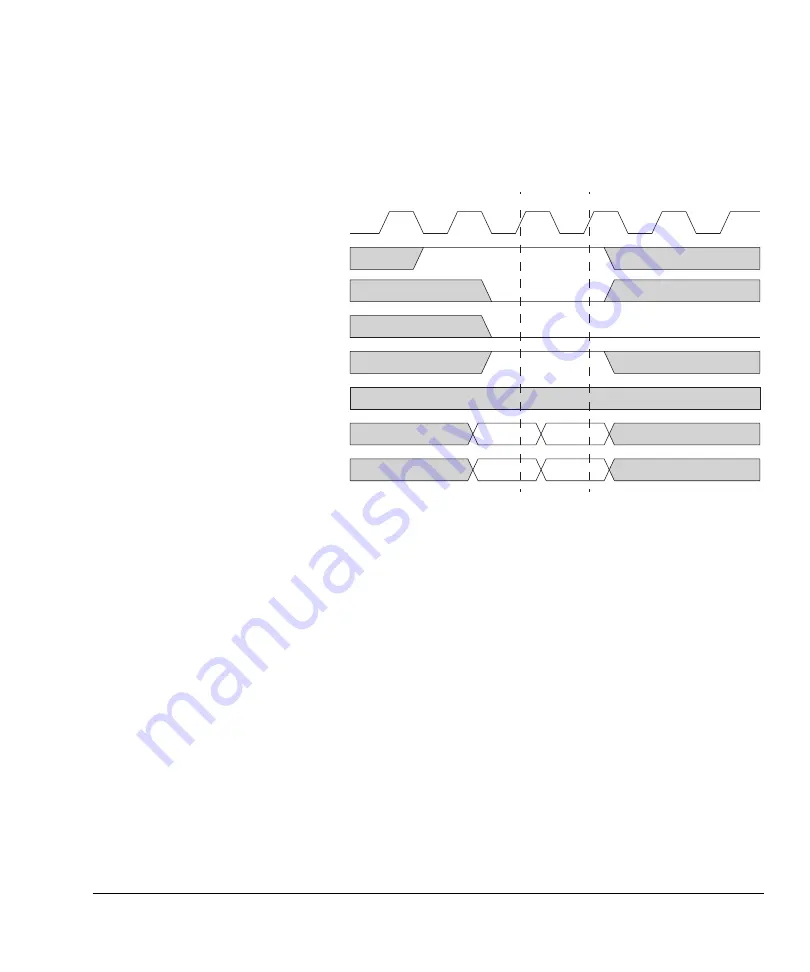

DMAReady

is redundant for dual-port RAM accesses and does not need to be sampled

by the DMA controller.

DMAENABLE

must be asserted one cycle prior to a request being made and can be

deasserted when

DMAnREQ

is taken HIGH after the last request.

Figure 5-6 Dual-port RAM DMA writes

5.2.5

Mixed read and writes

Figure 5-7 on page 5-10 shows:

•

an example of intermingled DMA read and write operations

•

that reads and writes can be performed back-to-back.

The behavior is the same for both single and dual-port RAMs. Depending on whether

the RAM was single or dual-port, the behavior of

DMAENABLE

,

DMAWait

, and

DMAReady

is described in sections

CLK

DMAENABLE

DMAnREQ

DMAWait

DMAnRW

DMAReady

DMAAddr

DMAWData

Write1

A1

A2

D1

D2

Write2

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...