Coprocessor Interface

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

7-11

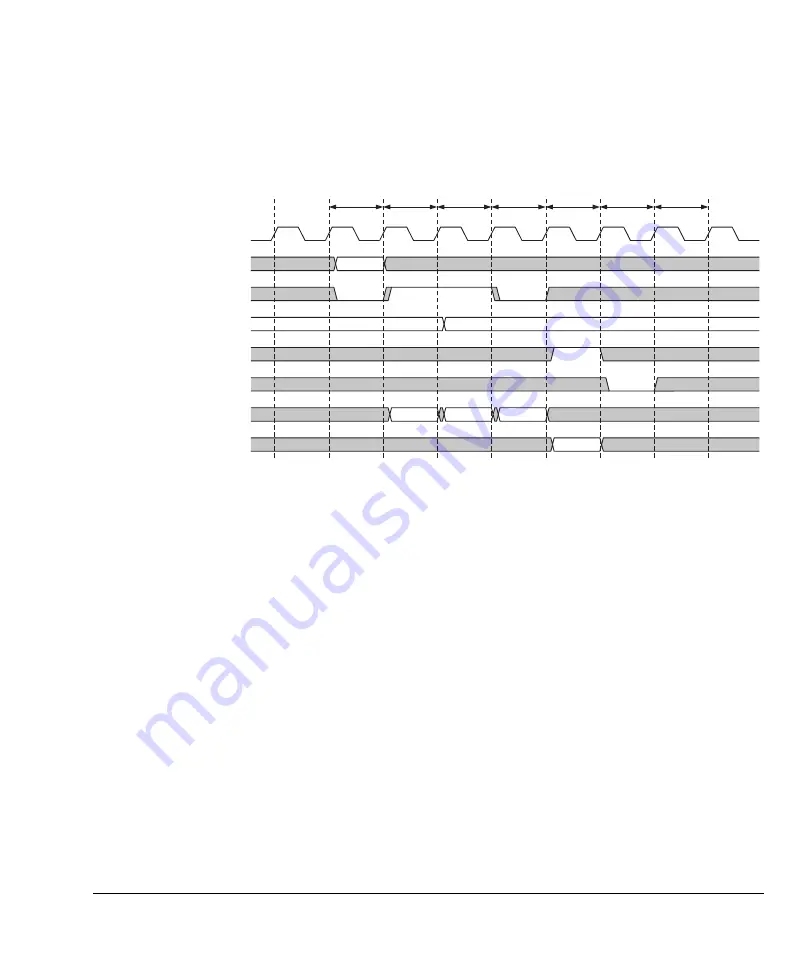

7.6

Privileged instructions

The coprocessor restricts certain instructions for use in privileged modes only. To do

this, the coprocessor tracks the

nCPTRANS

output. Figure 7-5 shows how

nCPTRANS

changes after a mode change.

Figure 7-5 Privileged instructions

The first two

CHSDE[1:0]

responses are ignored by the ARM9E-S because it is only

the final

CHSDE[1:0]

response, as the instruction moves from Decode into Execute,

that counts. This allows the coprocessor to change its response when

nCPTRANS

changes.

CLK

CPINSTR[31:0]

nCPMREQ

Fetch

Decode

Decode

Decode

Execute

Memory

CPRT

Coprocessor

pipeline

Write

CPPASS

CHSEX[1:0]

CPLATECANCEL

CHSDE[1:0]

Ignored

Ignored

Ignored

Old mode

New mode

nCPTRANS

LAST

Summary of Contents for ARM966E-S

Page 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Page 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...